#### Four-Terminal RF Phase Change Switches: Design, Optimization and Fabrication

Submitted in partial fulfillment of the requirements for

the degree of

Doctor of Philosophy

in

Electrical and Computer Engineering

Gregory P. Slovin

B.S., Electrical Engineering, University of FloridaB.A., Economics, University of FloridaM.S., Electrical Engineering, University of Florida

Carnegie Mellon University Pittsburgh, PA

December 2015

## Table of Contents

| Acknowledgements                                                               | 5  |

|--------------------------------------------------------------------------------|----|

| Abstract                                                                       | 7  |

| Chapter 1: Introduction                                                        | 9  |

| 1.1 Motivation                                                                 | 9  |

| 1.2 RF Switch Technologies                                                     |    |

| 1.3 Phase Change History and Physics                                           |    |

| 1.4 RF Phase Change Switches                                                   | 16 |

| 1.5 Thesis Outline                                                             |    |

| Chapter 2: Phase Change RF Switch Design Considerations and Impact on Efficacy |    |

| 2.1 Abstract                                                                   |    |

| 2.2 Introduction                                                               |    |

| 2.4 Model Setup                                                                |    |

| 2.5 Simulations of 3D Model vs. Measurement Results                            |    |

| 2.6 3D Model vs. 2D Model                                                      |    |

| 2.7 Simulation Results of Design Parameter Sweep                               |    |

| 2.8 Summary                                                                    |    |

| Chapter 3: Phase Change RF Switch Fabrication                                  |    |

| 3.1 Abstract                                                                   |    |

| 3.2 Introduction                                                               |    |

| 3.3 Standard Switch Process Flow                                               | 49 |

| 3.4 Notched Switch Process Flow                                                | 54 |

| 3.5   | Low Resistivity Tungsten Heater        | . 56 |

|-------|----------------------------------------|------|

| 3.6   | AIN Barrier Layer                      | . 61 |

| 3.7   | Low Resistivity GeTe                   | . 62 |

| 3.8   | GeTe Contact Resistance                | . 65 |

| 3.9   | Summary                                | . 67 |

| Chapt | er 4: DC Switch Characterization       | . 68 |

| 4.1   | Abstract                               | . 68 |

| 4.2   | Introduction                           | . 68 |

| 4.3   | DC measurement Test Setup              | . 69 |

| 4.4   | AlN Thickness Study, 105 nm vs. 170 nm | . 70 |

| 4.5   | The Effect of RF Gap                   | . 77 |

| 4.6   | GeTe 100 nm Thick                      | . 81 |

| 4.7   | AlN 200 nm Thick                       | . 89 |

| 4.8   | Summary                                | . 91 |

| Chapt | er 5: RF Switch Characterization       | . 93 |

| 5.1   | Abstract                               | . 93 |

| 5.2   | Introduction                           | . 93 |

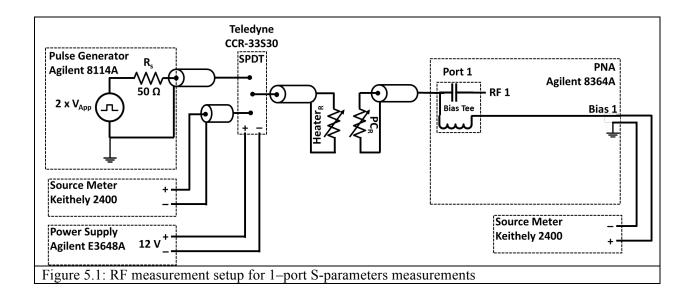

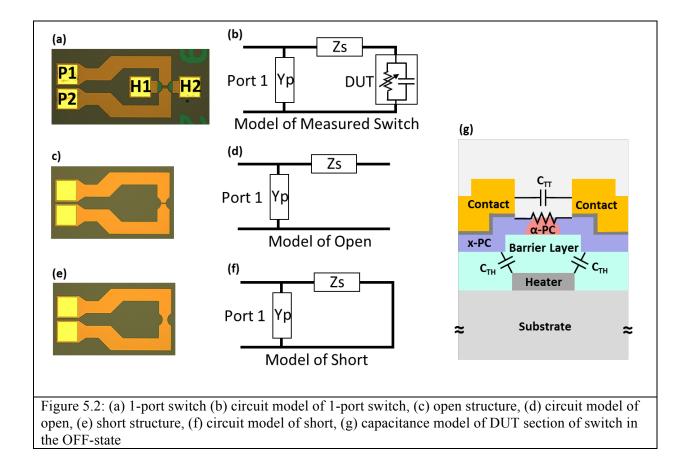

| 5.3   | One-Port S-Parameter Measurement Setup | . 94 |

| 5.4   | AlN Thickness Study, 105 nm vs. 170 nm | . 97 |

| 5.5   | The Effect of RF Gap                   | . 98 |

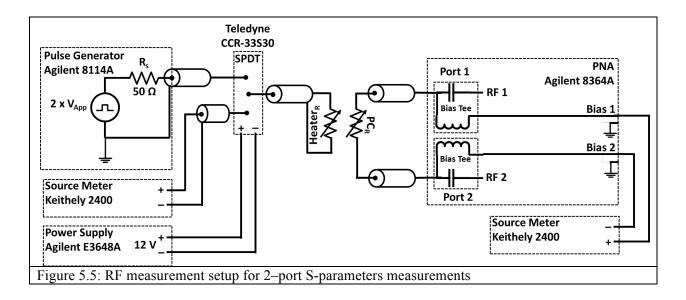

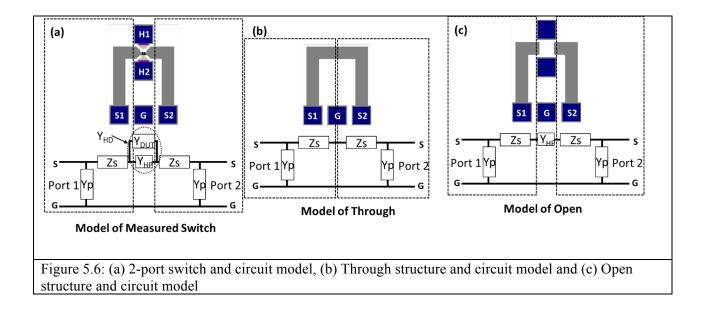

| 5.6   | Two-Port S-Parameter Measurement Setup | . 99 |

| 5.7 GeTe 100 nm Thick                        |  |

|----------------------------------------------|--|

| 5.8 AlN 200 nm Thick                         |  |

| 5.9 Switch Dimension Comparison              |  |

| 5.10 Summary                                 |  |

| Chapter 6: Integration with RF CMOS Circuits |  |

| 6.1 Abstract                                 |  |

| 6.2 Introduction                             |  |

| 6.3 Flip Chip Solder Bump Bonding Process    |  |

| 6.4 LC-VCO                                   |  |

| 6.5 3/5 GHz LNA                              |  |

| 6.6 Summary                                  |  |

| Chapter 7: Conclusions and Outlook           |  |

| 7.1 Conclusions                              |  |

| 7.2 Future Work                              |  |

| 7.3 Contributions and Publications           |  |

| Appendix                                     |  |

| References                                   |  |

## Acknowledgements

I would first like to thank my advisor, Prof. Jim Bain, for his continuous support and patience during my Ph.D research. His immense knowledge and positive thinking encouraged me even when I though all hope was lost. I would also like to thank my co-advisor, Prof. Ed Schlesinger. Although he was extremely busy, he helped me advance my research with both his knowledge and financial support. In addition, I want to express appreciation to the other committee members, Prof. Jeyanandh Paramesh and Dr. Rob Young. They continuously demonstrated a vested interest in my success and provided feedback on my research throughout the project.

I would also like to thank DARPA (Defense Advanced Research Projects Agency) as this work was supported, in part, by the Defense Advanced Research Projects Agency RF-FPGA program under contract HR0011-12-C-0095 and, in part, by an ONR DURIP equipment grant, Grant #N000141310874. I appreciate the efforts of Prof. Jim Bain who worked to obtain funding from the ONR DURIP equipment grant to purchase the AJA sputtering chamber. That chamber was vital to the success of my Ph.D research. Without it, I could not have achieved the high quality W and GeTe that were required to build a working switch.

I would also like to thank my fellow students who I had the pleasure of working with during my time in the MISCIC and RF-FPGA project. Mohammad Noman offered many words of wisdom during the first few years of my Ph.D studies and valuable advice regarding strategies that would enable me to complete my degree. I would like to express appreciation to my office mates, Min Xu, Abhishek Sharma and Nabil El-Hinnawy for our amazing discussions on phase change and threshold switching phenomenon. In addition, I would like to thank the CMU Nanofab staff members Chris Bowman, Carsen Klien, Dr. Matt Moneck and Norm Gottorn for their help with the equipment in the cleanroom. Last, but not least, I would like to thank my family and friends of their continuous support over this long, tortuous journey. I would like to thank my parents, Howard and Judy Slovin, for their emotional and financial support. I also appreciate the time my mom spent reading and reviewing my thesis. I would also like to thank my sister, Dr. Sara Slovin, and my girlfriend, Ms. Melody Albarran, who were continuously supportive of me.

### Abstract

The programmability of the optical and electrical characteristics of chalcogenide PC materials using joule heating makes them useful for data storage and memory applications. This work explored the use of PC materials in RF switches. A 4-terminal RF PC switch that used a separate tungsten microheater to program the PC material was designed, optimized, fabricated and integrated with an RF CMOS circuit.

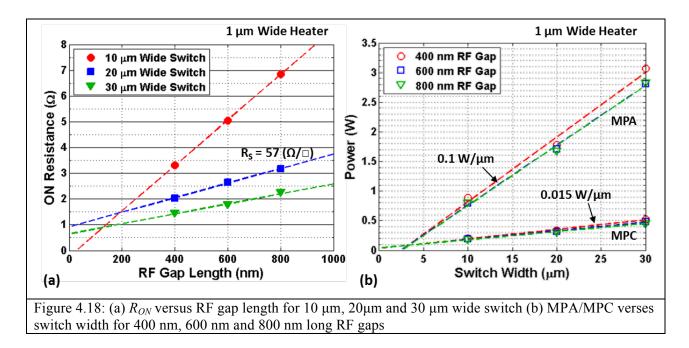

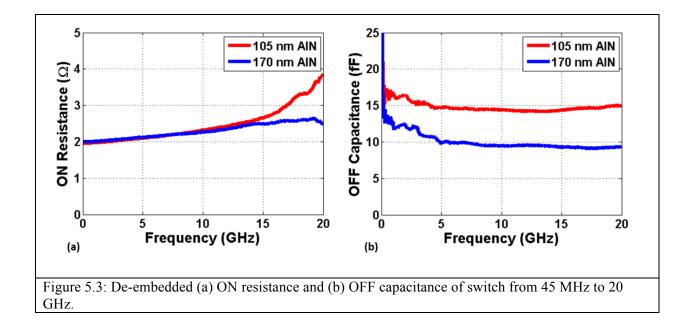

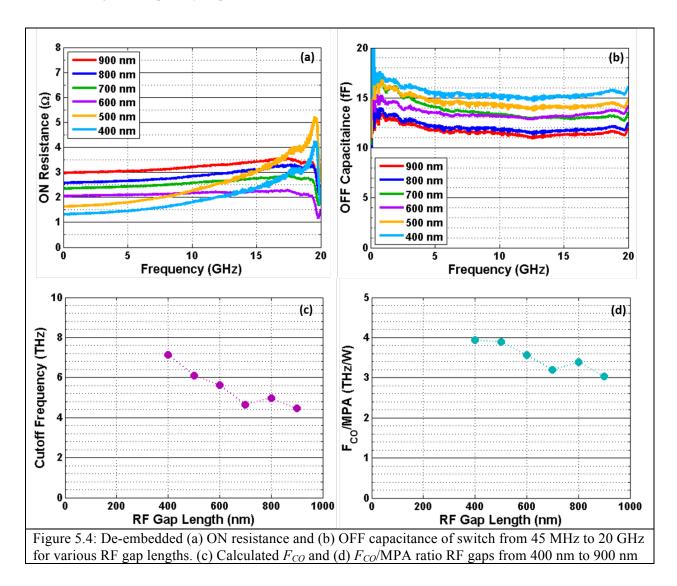

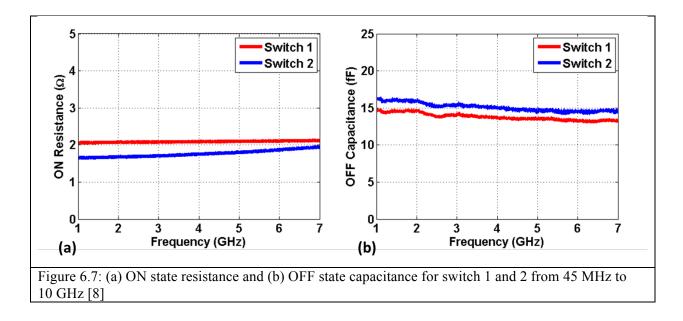

RF switches require a low ON-state resistance (< 1  $\Omega$ ) while maintaining a high ON-OFF ratio (10<sup>4</sup>). A low resistivity (1.5 x 10<sup>-6</sup>  $\Omega$ -m) PC material, GeTe, was developed to achieve an ON-state resistance of 1  $\Omega$ . The use of an AlN high thermal conductivity barrier layer was also introduced to improve the RF isolation and reduce the OFF-state capacitance ( $C_{OFF}$ ) to as low as 10 fF. These improvements in the materials enabled an RF switch cutoff frequency ( $F_{CO}$ ) of 9.6 THz.

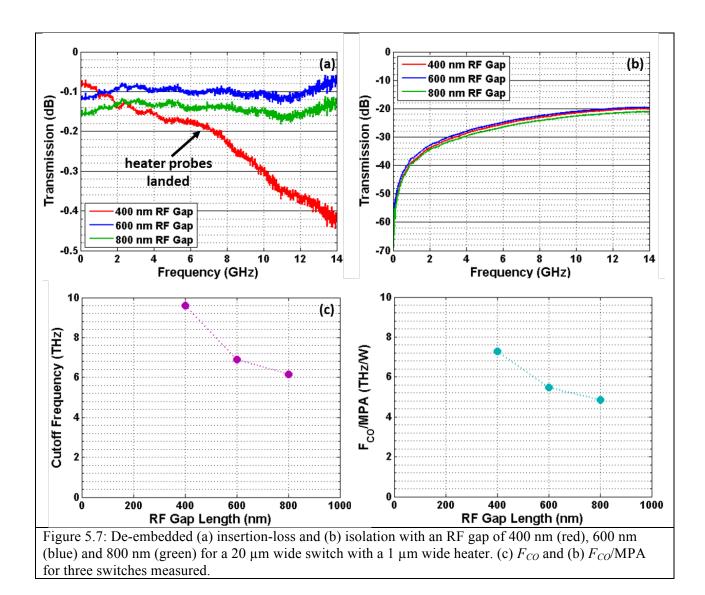

The effects of RF gap length and AlN barrier layer thickness on the RF performance were also explored in detail. Reducing the RF gap length, from 900 nm to 400 nm, increased the  $F_{CO}$  from 4.5 THz to 7.2 THz despite an increase in  $C_{OFF}$  from 11.7 fF to 15.4 fF. Increasing the AlN barrier layer thickness also improved the RF performance of the switch by reducing the capacitance attributed to the presence of the heater; however, this was at the cost of increasing MPA. Measurement results showed that increasing the AlN thickness above 170 nm does not further reduce  $C_{OFF}$  (10 fF). Therefore, increasing the AlN thickness any further only results in an increase in MPA with no additional improvement in  $F_{CO}$ .

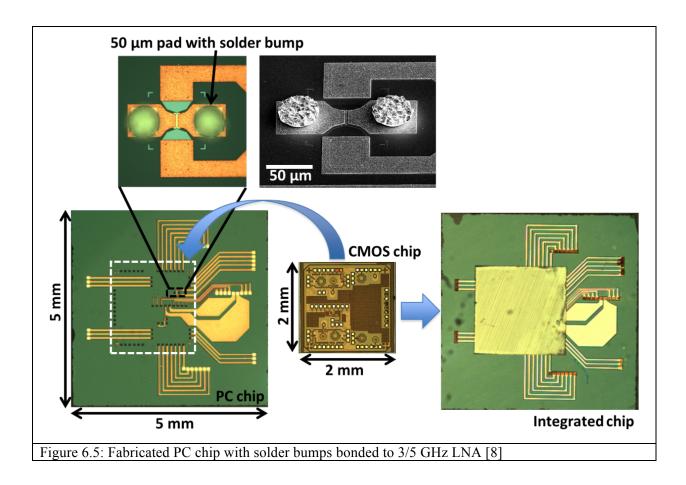

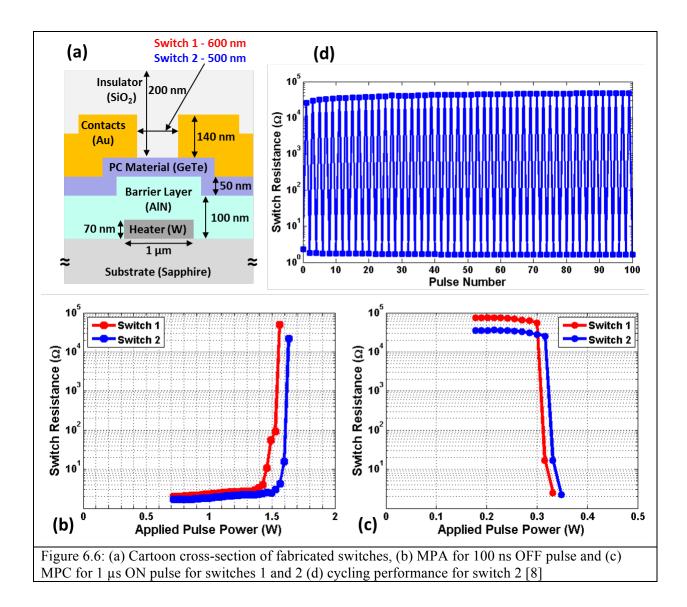

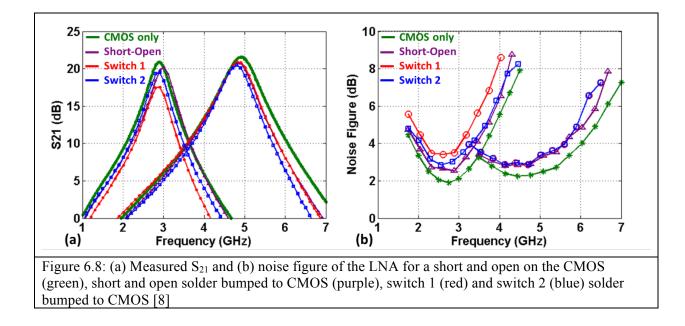

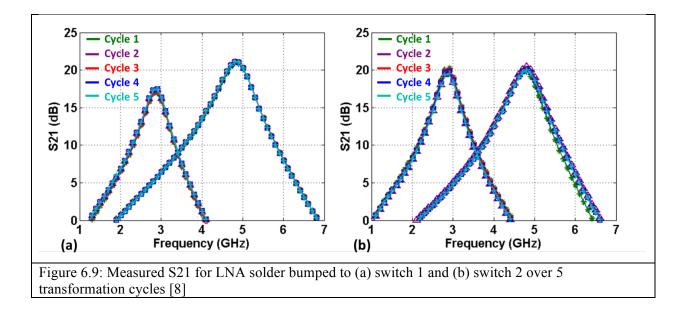

These switches were also integrated with a CMOS low-noise amplifier (LNA) using a custom flip chip solder bump bonding process to allow for *in-situ* reconfiguration between the 3 GHz and 5 GHz modes. The gain of the 3/5 GHz LNA was not significantly affected by the presence of the switch and solder bumps. It was approximately 20 dB in both modes of operation. The noise figure of the LNA in the 3 GHz mode increased from 1.9 dB to 2.85 dB due to the presence of the switch and solder bumps.

However, 0.65 dB can be attributed to the solder bumps, resulting in the switch only degrading the noise figure of the LNA by 0.3 dB.

## Chapter 1: Introduction

#### 1.1 Motivation

Wireless communication is all around us, from cellular phones to satellite television, and most people come into contact with it every day. Data can be transmitted to our phones, computers, cars and televisions using radio frequencies. Specialized electronic circuits (Radio Frequency (RF) circuits) are used to transmit and receive this wireless data which allows us to perform such diverse activities as transmitting personal location information to a network of satellites to checking the scores of last night's basketball games on our smart phone while walking the dog. There are over 25 radios in the iPhone 6 that are used for various cellular bands (i.e. 3G, LTE), WiFi, GPS, Bluetooth and more. Each wireless communication standard requires its own special radio that is designed for a small band of frequencies at which that standard operates. There are 44-frequency bands that are used for the LTE wireless standard [1]. However, the iPhone 6 from AT&T only has the ability to operate on 16 to 20 of those bands due to the space the necessary radio occupies for each band [1]. A single narrow band RF circuit is used to for each frequency band because the incoming signals are at frequencies in the gigahertz range, only operate with a few pico-Watts of power and are at the same time being mixed with many other RF signals [1]. Due to these factors, a single wideband RF circuit cannot be used to achieve the required performance to operate at these wireless standards.

A great solution for space limitations inherent in wireless devices would be designing a switch that would work for these high frequency signals and would allow for the re-configurability of RF circuits that would otherwise not be possible. Some of these switches are already present in our smart phones, enabling the hardware to switch an antenna between transmit and receive RF circuitries. Further integration of RF switches in RF circuits would allow for reconfigurable radios that could operate at numerous frequency bands while still maintaining high performance. By combining multiple radio standards together, a smaller form factor can be achieved, thus reducing costs [1]. Reconfigurable radios would also allow users to have access to more wireless standards that otherwise would not be possible due to space constraints. RF switches could enable mobile devices to adapt to future radio standards thereby increasing the device's lifespan [2]. RF switches have already been demonstrated in many other RF components such as a reconfigurable inductors [3], LC-VCOs (inductive-capacitive voltage controlled oscillators) [4], antennas [5], phase shifters [6], power amplifiers (PA) [7] and LNAs (low noise amplifiers) [8].

#### 1.2 RF Switch Technologies

The goal of an RF switch is to allow the RF signal to pass through when the switch it is in the ON-state and block the RF signal when it is in the OFF-state. This can be done in one of three configurations: series, shunt and series shunt. In a series configuration (fig. 1.1(a)), the switching lies in the RF signal path. For a shunt configuration (fig. 1.1(b)), the switch turns on and off a shunt path to ground. When the switch is in the ON position, the RF signal is shunted to ground preventing the RF signal from propagating further. A series-shunt configuration (fig. 1.1(c)) combines both of these features to improve the RF performance. Two switches are used in conjunction to either allow the RF signal to pass through or to route the RF signal to ground.

This thesis will only demonstrate switches in the series configuration. The RF switch performance can be determined by measuring the insertion loss of the switch in the ON-state and the isolation of the switch in the OFF-state. The figure of merit of RF switches is their cutoff frequency ( $F_{CO}$ )

using their ON-state resistance ( $R_{ON}$ ) and OFF-state capacitance ( $C_{OFF}$ ). The F<sub>CO</sub> is defined as the frequency at which the magnitude of the switch impedance in the ON-state is equal to the magnitude of the switch impedance in the OFF-state ( $1/(2\pi \times R_{ON} \times C_{OFF})$ ). RF switches require a low  $R_{ON}$  (< 1  $\Omega$ ) while maintaining a high ON-OFF ratio ( $R_{OFF}/R_{ON} \ge 10^4$ ) and a low  $C_{OFF}$  (<15 fF) for use in reconfigurable RF circuits. Some examples of working RF switch technologies are: MEMS (micro electrical-mechanical systems), PIN (p-type semiconductor, intrinsic semiconductor, n-type semiconductor) diodes, HEMTs (high electron mobility transistors), CMOS (complementary metal oxide semiconductor) and Phase Change (PC). The state of the art of each of these will be discussed below.

MEMS switches are voltage controlled and require large voltages to mechanically actuate a lever that makes mechanical and electrical contact. RF MEMS switches requires 20-80V to turn the switch on but uses little to no current while having a  $C_{OFF}$  of 2-4 fF [9]. An SP3T (single poll – triple throw) has been demonstrated using a 65 V actuation voltage with insertion loss of less than 0.8 dB and isolation over 25 dB up to 20GHz [10]. A shunt RF MEMS switch with actuation voltages of less than 15V has been demonstrated [11]. The MEMS switch lifetime can be as high as 7 billion cycles with an insertion loss of less than 0.1 dB and 20 dB of isolation up to 40GHz [11]. RF MEMS switches have been used to create 2 and 4-bit TTD phase shifters with an  $R_{ON}$  of approximately 1  $\Omega$  [6]. RF MEMS switches have also been used to tune matching networks for a multiband LNA and PA [7]. Besides the large actuation voltage required to turn the switch on, another disadvantage is their large size as RF MEMS switches are typically a few hundred microns a side.

PIN diodes have also been used as RF switches [5], [12]. They act as a current controlled variable resistor with a higher bias current, which results in a lower  $R_{ON}$ . AlGaAs PIN diodes in a single pole double throw (SPDT) configuration have been shown to exhibit a 0.6 dB insertion loss and over 35 dB of isolation at 40 GHz [12]. The PIN diodes require 10 mA of bias current in the ON-state and - 5 V of bias in the OFF-state [12]. The AlGaAs PIN diodes can operate with up to 26 dBm of incident power [12]. PIN diodes have been used to reconfigure an annular slot antenna [5]. In this instance, two

PIN diodes were used to configure the impedance matching circuit allowing the antenna to operate at 5.2, 5.8 and 6.4 GHz [5]. Two downsides to PIN diodes are that they need constant current whenever the switch is on and, as it is a two-terminal device, the RF signal and programing current must share the same path. This may limit where the switch can be used to reconfigure RF circuits.

HEMTs are popular choices for use as an RF switch because of they have higher mobility than traditional CMOS technology (resulting in lower  $R_{ON}$ ) and they have high power handling capabilities. A GaN HEMT on SiC has been demonstrated as an RF switch in an SPDT configuration that can handle large amounts of RF power [13]. A switch designed for frequency ranges from DC- 12 GHz has 1.0 dB of insertion loss and 16 dB of isolation and can up to handle 15 W of RF power [13]. These transistors are voltage controlled and have a pinch-off voltage of -4.2 V to turn the switch off [13].

Silicon analog hardware already exists in every system platform, therefore RF silicon switches are attractive due to their monolithic integration resulting in lower assembly costs. An SPDT using series shunt CMOS switches has been tested from DC to 60 GHz at the 45 nm node [14]. The switches were fabricated on an SOI substrate, to minimize substrate coupling, allowing for an insertion loss of 1.2 dB and an isolation of 33 dB at 20 GHz [14]. One major issue with RF CMOS switches is that, in order to reduce the  $R_{ON}$  of the switch to 1  $\Omega$ , an extremely wide device must be made. The resulting CMOS switch at the 45 nm node will have an  $F_{CO}$  of less than 2 THz [4].

RF switches using PC (chalcogenide) material have shown promising results. These switches use the resistance change between the crystalline (low resistance) and amorphous phases (high resistance) to turn the switch on and off, respectively. An SPDT using series shunt PC switches has been demonstrated to have an insertion loss of 0.2 dB and an isolation of 38 dB [15]. Unlike the other RF switches previously discussed, PC switches are non-volatile and only require power to switch between states, not to maintain a particular state. The transformation voltages can be as high as 19 V [16], but that can be reduced by sizing the device. These switches can be designed to be 4-terminal devices, thereby separating the control (programming) signal from the RF signal. This, in conjunction with their smaller size (30 µm on a side), makes them a promising candidate for integration into RF circuits. RF PC switches have been used to reconfigure inductors [3], [17]. They have also been used to reconfigure a wide tuning range LC-VCO [4] and a 3/5 GHz LNA [8].

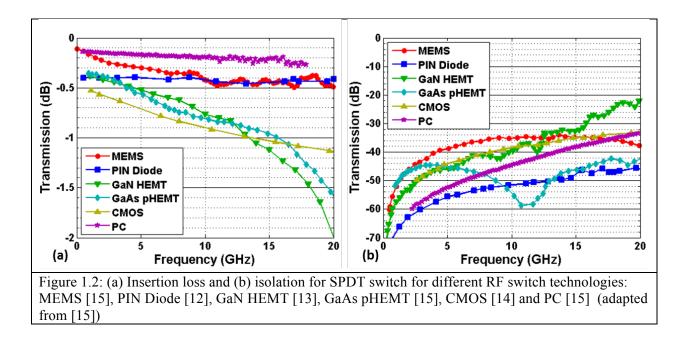

Fig. 1.2 shows the insertion loss and isolation data for SPDT switches using the different RF switch technologies discussed above. The PC RF switch has the lowest insertion loss compared to all switch technologies while still maintaining adequate isolation. Four-terminal RF PC switches show the most promise for integration in reconfigurable RF circuits because they are non-volatile and have a small footprint compared to the other technologies.

#### 1.3 Phase Change History and Physics

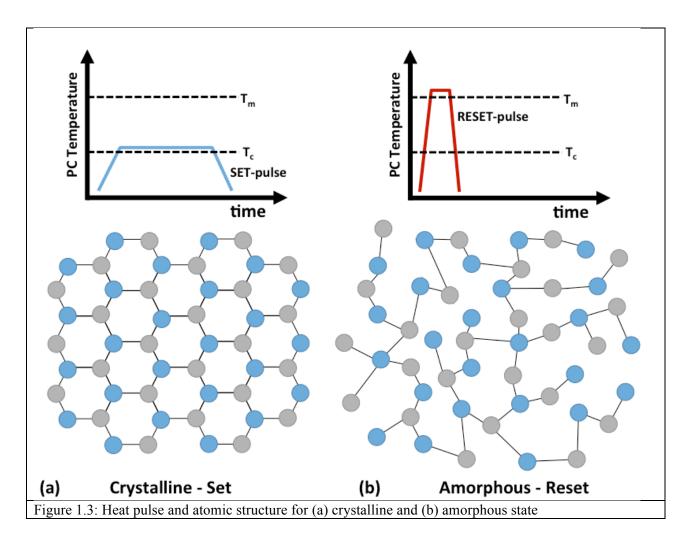

In 1968, Ovshinsky first discovered reversible electronic switching from a highly resistive state to a conductive state with the application of an electric field in an evaporated GeAsSiTe thin film [18]. These materials became known as phase change (PC) materials because they consist of an amorphous high resistivity phase and a crystalline low resistivity phase. The PC material is switched between states through the use of heat pulses. To crystalize the PC material, a heat pulse is applied to raise its temperature above the crystallization temperature long enough to allow for the material to crystallize (fig. 1.3(a)). In order to amorphize the material, a short heat pulse is applied to melt the PC material which is then it is quickly quenched to prevent reordering of the crystal lattice (fig 1.3(b)).

PC materials also have a change in their optical properties that is associated with their shift in phase. In the crystalline phase, the material has high reflectivity, and in the amorphous phase, it has low reflectivity [19]. Optical data storage systems use PC materials in CD-RW and DVD-RW, exploiting the difference in reflectance between the crystalline and amorphous state to store data [19]. A fast, high power laser or current pulse is used to amorphize the phase change material which results in it having a

low reflectivity and high resistivity [20]. A longer, lower power laser or current pulse is used to crystalize the material which results in it having high reflectivity and low resistivity [20].

In 1986, Te-Ge-Sn-Au thin films were demonstrated for use in rewritable disk media [21]. Crystallization of the phase change material was obtained using a 1  $\mu$ s, 2 mW laser pulse with the amorphization requiring a 0.2  $\mu$ s, 6 mW laser pulse [21]. Laser pulses as short as 120 fs have been used to create amorphous marks in optical media that contains GeSbTe as the PC material for use in RW-DVDs [22].

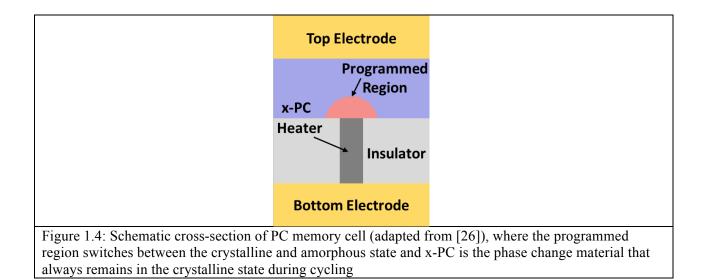

PC materials have also been used as resistive memory cell, where the resistance of the memory cell in the crystalline state is a "1" and the resistance in the amorphous state is a "0". Unlike in optical media, the memory cells are not programmed by using laser pulses, but instead by passing current though the PC material and inducing joule heating [19]. When the PC material is in the amorphous phase, threshold switching is needed to allow for enough current to flow in order to cause joule heating and allow for permanent memory switching [19], [23], [24]. To aid in heating of the PC material, a heater is placed in series with the memory cell as seen in fig. 3. The PC material that transforms between the ON (low resistance) and OFF (high resistance) state is mushroom shaped just over the heater (fig. 1.4). This topology is not preferred to be used as an RF switch due to the additional series resistance of the heater. In addition, the RF signal and programing signal share the same path. The resistance of the memory cell in the ON-state is about  $2 k\Omega$  due in part to the additional resistance of the heater [25].

Choosing an appropriate PC material for use in an RF switch is critical in determining its performance. Not only is a large  $R_{OFF}/R_{ON}$  ratio (> 10<sup>4</sup>) important but so is the resistivity of the material in the crystalline state. The lower the resistivity of the PC material in the crystalline state, the smaller the switch can be made, resulting in a smaller C<sub>OFF</sub> and less power required to switch the device. GeSbTe (GST) is a common PC material used in PC memory; however, it only has a crystalline resistivity of  $2x10^{-4} \Omega$ -m. On the other hand, GeTe has been reported to have a resistivity that is almost two orders of magnitude lower [27]–[29]. This difference in resistivity results in PC memory cells having a lower ON resistance (30  $\Omega$  vs. 2 k $\Omega$  for GST) that can be cycled up to  $10^5$  times [25]. While this is not as high as GST (> 10<sup>7</sup>), it still demonstrates preliminary reliability for us as an electronic switch.

#### 1.4 RF Phase Change Switches

#### 1.4.1 Via Style PC Switch

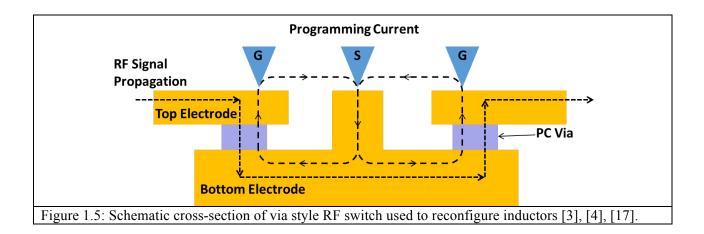

There are three different types of RF PC switch configurations: via style, direct heating and indirect heating. Via style RF switches have been demonstrated many times [3], [4], [17], [29], [30]. They are similar to a PC memory cell without the series heater (fig. 1.5). Via style RF switches are

popular because they are easily to fabricate and can be easily integrated into a backend CMOS process. However, these switches have two main problems: the RF and programming signal share the same path and they are difficult to fully crystalize due to filament formation [24], [29], [31]. The places where the via style switches can be used in RF circuits are limited because the RF and programming signal share the same path. Fig.4 shows the configuration the via style switches used to reconfigure inductors in an LC-VCO [4]. The programming current comes from the middle terminal using microwave (Ground-Signal-Ground) probes (fig. 1.5). In a fully implemented system, these probes would need to be replaced with MEMS probes. The use of transistors instead of probes to transform the PC material (drive current off 100 mA for two switches [29]) would result in at least 100 fF of additional capacitance that would degrade the RF performance of the switch. These switches are difficult to fully crystalize due to filament formation through the amorphous material [29], [31]. As discussed earlier, a threshold switching event must occur first in the amorphous region before enough current is allowed to pass through and cause enough joule heating to occur to crystalize the material [19], [23], [24]. The threshold switching event occurs at the weakest amorphous region and depends on the amorphous region's size and shape [24]. This can lead to the formation of a crystalline firmament thought the amorphous region [24], [29], [31]. However, multiple pulses can be used to fully crystalize the material [3].

#### 1.4.2 Direct Heating PC Switch

A heater in direct contact with the PC material can be used to prevent the filament formation and to separate the programming path from the signal path. Carbon nanotubes have been used in direct contact with PC memory cells to reduce programming currents [32]–[34]. A 4-terminal RF switch has been demonstrated to have 0.6 dB of isolation in the ON-state and 20 dB of insertion loss at 20 GHz resulting in a 3.7 THz switch [35]. The device is set up similar to a via style switch except the RF signal propagates horizontally thought the device while the programming current travels vertically though the device. This design may still have the issue of filament formation vertically in the device, making it difficult to fully turn on. By placing the heater in direct contact with the phase change, the power required to switch the device is less than 100 mW [35]. The downside to this design is that the heater is still electrically coupled to the RF switch. This results in a shunting of the RF signal to ground though the heater. To mitigate that effect, a high resistance heater must be used. This results in larger programming voltages (16 V) [35].

#### 1.4.3 Indirect Heating PC Switch

The use of indirect heating can solve many of the problems seen in via style and direct heating RF switches. A micro-heater separated by a dielectric barrier layer can be placed above or below the PC material and can be used to switch the device. The use of a 1  $\mu$ m thick Pt heater on top of a lateral PC memory cell was shown to crystallize the PC material and was separated by a SiO<sub>x</sub>/SiN barrier layer [36], [37]. However, the heater had a 10  $\mu$ s time constant and only reached temperatures up to 270 °C, making it impossible to turn the switch off [36], [37].

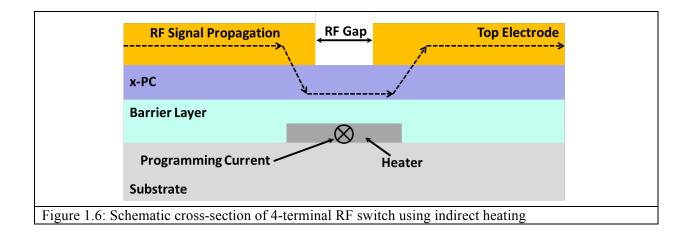

For an RF switch with an indirect heater, turning the switch off can require up to 4 W of power [38] while less than 100 mW [35] is required for a switch with a direct heater. A micro-heater is separated from a PC layer by an electrically insulating barrier layer (fig. 1.6). The heater is used to transform the PC material between the amorphous and crystalline phases. The RF signal propagates across one electrode down into the PC material and then back up to the other electrode. Enough current must flow though the micro-heater for it to reach temperatures greater than the melting temperature of GeTe (723 °C [39]). The addition of the dielectric barrier layer between the heater and the PC layer results in the heater needing to reach temperatures in excess of 1000 °C to successfully melt the phase change material. This can require power ranging between 0.5 W to 4 W, depending on the pulse length [38]. The cooling time of the system is also important for these switches. To amorphize the PC material, it must first be melted and then quickly quenched below the crystallization temperature  $(185 - 200 \,^{\circ}\text{C})$ [27] [29]). The quench time required for the switch is dependent on the crystallization time of the PC material. It has been reported that the crystallization time for GeTe can be as fast as 16-30 ns [40]–[43] and is very dependent on the stoichiometry of the GeTe [41] [43]. The switches in this thesis were designed to have a cooling time (time from melting temperature to crystallization temperature) of less then 100 ns to ensure they could be amorphized.

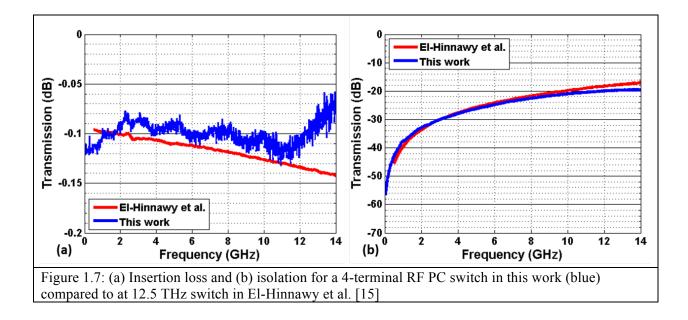

The best in class 4-terminal RF switch has reported an  $F_{CO}$  of 12.5 THz [15] with an insertion loss of 0.16 dB and an isolation of -15 dB at 20 GHz [15]. This particular switch is 30 µm wide with an RF gap (fig 5) of 0.9 µm [15]. A NiCrSi micro-heater with SiN<sub>x</sub> dielectric barrier is used in this switch. This thesis seeks to improve upon this state-of-the-art switch by developing a low resistivity W microheater, AlN barrier layer and lower resistivity GeTe and then integrating these components into the switch. Fig. 6 compares the insertion loss and isolation of a 4-terminal RF PC switch from this work to El-Hinnawy et al. [15]. The insertion loss for both switches is similar while the isolation is slightly higher in this work (19.6 dB vs. 17.1 dB at 14 GHz). The switch in this work is only 20 µm wide (vs. 30 µm) and therefore takes less power to switch the device. Therefore, this thesis does make significant advancements to the state-of-the-art RF PC switch.

#### 1.5 Thesis Outline

The rest of the thesis will discuss the details of these switch advancements. Chapter 2 will discuss how to accurately model the thermal response of the switch. It will show the effects of changing the width of the heater, RF gap length and barrier layer thickness as well the use of a notch in the PC layer to reduce the power required to switch the device. Chapter 3 will discuss the process flow used to

fabricate the switch and will detail the improvements made in the heater, barrier layer and PC material. Chapter 4 will show the DC measurement setups used to test the fabricated switches. It will compare  $R_{on}$  for different switch layouts and the respective power required for switching. The effect of AlN thickness, RF gap length heater width and switch width will all be examined. Chapter 5 discusses the RF measurement setup as well as the RF performance of the switches measured in Chapter 4. Chapter 6 will show the process used to integrate these switches with RF CMOS circuits to create an LC-VCO and a 3/5 GHz LNA. It will also attempt to differentiate the effect of the solder bump boding process from the PC switch on the RF performance of the LNA. Finally, Chapter 7 will summarize all the advancements made in this thesis and what further steps can be taken to improve the performance of the switch.

# Chapter 2: Phase Change RF Switch Design Considerations and Impact on Efficacy

#### 2.1 Abstract

In this chapter, a 3D model of a 4-terminal inline RF phase change switch is simulated and matched to measurement results. Temperature dependent thermal and electrical properties were included to insure the model's accuracy. Once the accuracy of the model was validated, a less complex 2D model was used to more quickly scan the design space and determine the effect of RF gap length, heater width and barrier layer thickness on minimum power to amorphize (MPA) and cutoff frequency ( $F_{CO}$ ) of the switch. From the simulation results, the RF gap has the largest impact on RF performance. Reducing the RF gap length from 900 nm to 100 nm increases the  $F_{CO}$  from 15 THz to 45 THz with a 50% increase in MPA. This increase in MPA can be mitigated with the use of a notch design. The use of a notch is more efficient in reducing the MPA than increasing the RF gap length. For the same MPA, the notched switch has an  $F_{CO}$  of 32 THz while increasing the RF gap results in an  $F_{CO}$  of 28 THz.

#### 2.2 Introduction

The ability to model and accurately simulate the electrical and thermal response of the 4-terminal RF PC switch is important in understanding the design limitations of the switch. While fabricating and testing RF switches is the only true way to determine the functionality and performance of a specific switch design, it can be a costly and time consuming processes. An accurate model and the ability quickly simulate many switch designs can be used to provide insight on how the functionality and performance of switch may change when sweeping a design space.

This chapter will discuss the design, modeling and simulation results of a 4-terminal inline RF phase change switch. The basic principles of the switch functionality will be explained followed by an explanation of the properties that were included in the model to ensure accurate results. Simulation results of a 3D model will be compared to the measurement results of a fabricated switch.

There are four design variables that affect the minimum power to amorphize (MPA), heater temperature, cutoff frequency ( $F_{CO}$ ) and current density in the heater which are: RF gap length, heater width, barrier layer thickness and notch depth. These specific parameters will be defined, analyzed and discussed in detail below. In addition, the effects of increasing amorphization pulse width on MPA, heater temperature and cooling time will be shown.

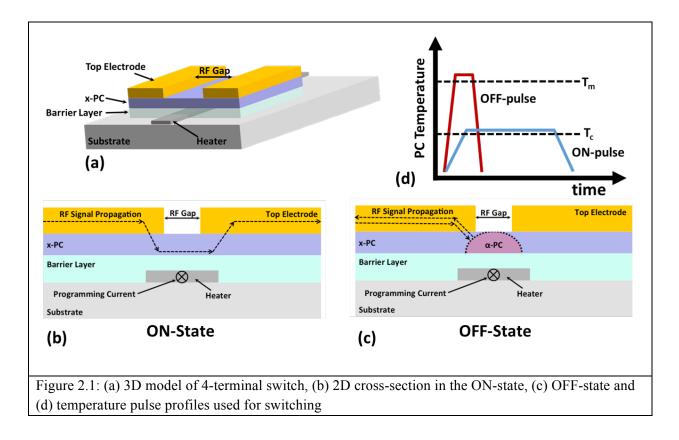

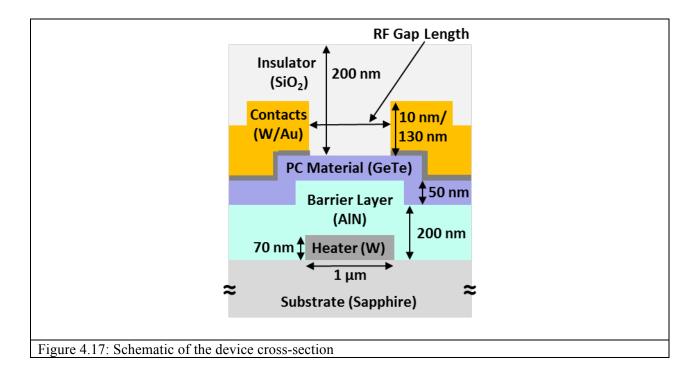

#### 2.3 RF Phase Change Switch Design

Fig. 2.1(a) shows the basic design of the switch. A thin film resistor which acts as a heater is placed on top of an electrically insulating substrate. A dielectric barrier layer is placed between the heater and the PC material. Metal electrodes on top of the PC material are then used to define the switch. The length of the RF gap is the main determining factor of the switch resistance in the ON-state. In the ON-state (fig. 2.1(b)), the RF signal propagates though the top electrode down into the crystalline PC-material then back up to the top electrode. In the OFF-state (fig. 2.1(c)), the RF signal propagates through the top electrode, then hits the amorphous PC-material and reflects back. The heater is used to transform the switch between the two states. The heat generated in the heater must flow across the barrier layer to raise the temperature of the PC-material. The presence of the barrier layer does result in an inefficient heating of the PC-material but is necessary in order to separate the RF signal path from the programming path.

By forcing current through the heater, the PC-material in the RF-gap can be heated allowing for transformation between the crystalline ON-state and the amorphous OFF-state. The heating profiles are shown in 2.1(d), where a wide pulse (blue) is used to raise the temperature of the PC-material above the

crystallization temperature and is then held there long enough to completely crystalize the material in the RF gap. A narrow pulse (red) is used to quickly raise the temperature of the PC-material in the RF gap above the melting temperature and which is then quickly quenched to ensure the PC-material is in the amorphous state. The effect of the OFF-pulse width will be discussed later in the chapter.

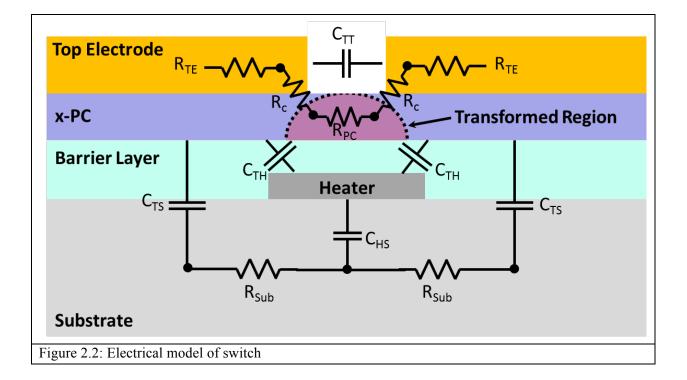

The material choices for the barrier layer and the PC-material are most critical in order to maximize the performance of the switch. The resistivity of the PC-material most directly contributes to the ON-state resistance of the switch while the dielectric constant of the barrier layer most directly contributes to the OFF-state capacitance. In the electrical model of the switch (fig. 2.2), the resistance of the switch is comprised of 3 parts: the top electrodes ( $R_{TE}$ ), the contact resistance between the switch and the PC-material ( $R_c$ ) and the resistance of the PC-material in the RF-gap ( $R_{PC}$ ). The non-transformed material is in the crystalline state to assure the lowest ON-state resistance possible. Because the top electrode is a highly conductive metal such as Au,  $R_{TE}$  has a minimal contribution to the total resistance of

switch. By choosing a proper contact metal and maintaining a pristine interface between the top electrode and PC-material,  $R_c$  can also be minimized which leads to  $R_{PC}$  being the largest contributor to the resistance of the PC switch.

Choosing an appropriate material for the PC layer is also critical. GST is a common PC-material used in phase change memory (PCM) but has a resistivity of  $5 \times 10^{-4} \Omega$ -m [25]; however, GeTe has a resistivity that is over two orders of magnitude lower than GST of  $3-4 \times 10^{-6} \Omega$ -m [25], [29], [44], and is shown to be more suitable in RF PC-switch applications [29], [44]. A resistivity as low as  $1.5 \times 10^{-6} \Omega$ -m for GeTe films has been achieved in this work and will be discussed in more detail in a later chapter.

The capacitance of the switch in the OFF-state is comprised from 3 main sources: the capacitance between the traces and heater to the substrate ( $C_{TS}$ ,  $C_{HS}$ ), the capacitance between the two traces ( $C_{TT}$ ) and the capacitance between the trace and the heater ( $C_{TH}$ ). By choosing an electrically insulating substrate such as sapphire,  $R_{Sub}$  is large and thereby minimizes the contributions of  $C_{TS}$  and  $C_{TH}$  to the overall OFF-state capacitance of the switch.  $C_{TT}$  is determined by the RF gap length with a longer

RF gap resulting in a lower  $C_{TT}$ ; however, this is at the expense of  $R_{PC}$  and is therefore difficult to reduce. The capacitance between the heater and the traces  $C_{TH}$  is a function of the heater width as well as the thickness and dielectric constant of the barrier layer. The size effect of the heater will be discussed later in the chapter. The choice of dielectric material for the barrier layer is not as simple as choosing one with the lowest dielectric constant to minimize  $C_{TH}$ , because not only does the barrier layer have to electrically isolate the heater from the RF signal path but it also must allow heat to flow from the heater to the PCmaterial. Therefore, the thermal conductivity  $(k_{th})$  of the barrier layer must also be considered. In previous examples of 4-terminal RF phase change switches [15], [16], [38], SiN<sub>x</sub> is used as the barrier layer which has a relative dielectric constant of 7 [45]. The thermal conductivity of a 160 nm of  $SiN_x$ film, provided by El-Hinnawy of Northrop Grumman Electronic Systems, was measured to be 1.1 W/m-K using the frequency domain thermal reflectance (FDTR) technique [46]. Using a material with such a low k<sub>th</sub> will result in a large temperature gradient across the barrier layer thereby limiting heat flow to the PCmaterial. Using a dielectric with a higher  $k_{th}$ , such as AlN, will limit the thermal gradients across the barrier layer and may even allow the thickness of this layer to be increased far beyond what would be achievable using SiN<sub>x</sub>. AlN has a slightly higher dielectric constant of 8.0-9.2 [47], but has a bulk  $k_{th}$  of 285 W/m-K [48]. The  $k_{th}$  for sputtered AlN films has been measured to be as high as 130 W/m-K [49]. In the model that is simulated, a more modest value of 50 W/m-K is arbitrarily used and the simulation results are relatively insensitive for values above 10 w/m-K.

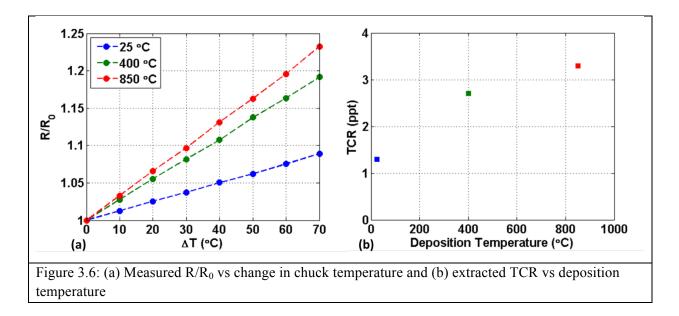

#### 2.4 Model Setup

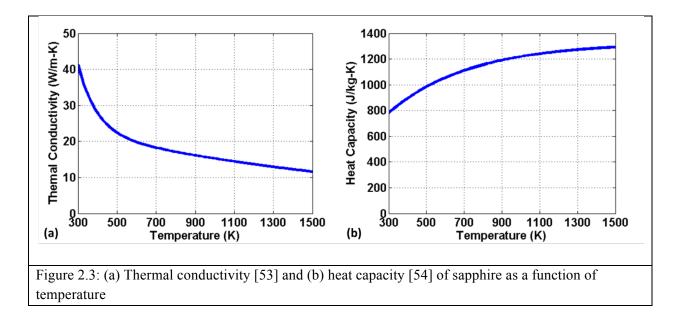

A 3D model of the 4-terminal inline RF phase change switch was built and simulated using COMSOL Multiphysics software. In order to simulate the thermal response of the switch, three physics modules including heat transfer, electric currents and electric circuits were used concurrently and were coupled to each other. The material properties required for the simulation were heat capacity ( $C_p$ ), density (rho), thermal conductivity ( $k_{th}$ ), relative permittivity ( $\epsilon_r$ ), resistivity at 300 K ( $\rho_{300}$ ) and temperature coefficient of resistivity ( $\alpha$ ). Some of these values were measured while others were taken from literature. There are a few main parameters that must be included in the model to ensure its accuracy. The measured resistivity and TCR of the W heater are required to ensure proper power dissipation during the voltage pulse across the heater. The temperature dependence of sapphire's  $k_{th}$  (fig. 2.3(a)) and  $C_p$  (fig. 2.3(b)) is needed for the heater to reach the required temperature necessary to melt the PC-material. A thermal interface layer between the W heater and sapphire substrate is also necessary for the heater to reach the desired temperature. A thermal conductance of 200 MW/m<sup>2</sup>-K is used for this interface and is based on the thermal conductance of Cu and Al with sapphire, 200-300 MW/m<sup>2</sup>-K [50] and 90 MW/m<sup>2</sup>-K [51], respectively. These two metals are chosen because their Debye temperatures (Cu – 343.5 K, Al – 428 K) are the closest match to W Debye temperature (400 K) [52].

A thermal interface layer of 200 MW/m<sup>2</sup>-K was also used between the AlN and sapphire; however, this did not significantly change the results. The thermal interface was kept in the model because it is known to exist despite not playing a significant factor simulation results. Temperature thermal conductivities for W and Au were also added and were based on the Wiedemann-Franz law [52] (eq. 2.1). The thermal conductivity at temperature ( $k_{th-T}$ ) is shown in eq. 2.1, where  $k_{th-300}$  and  $\rho_{300}$  are thermal conductivity and resistivity of the metal at room temperature, respectively. However, this does not significantly effect to outcome of the simulation.

$$k_{th-T} = \frac{k_{th-300} \times \rho_{300}}{\rho_{300}(1+\alpha\Delta T)}$$

(2.1)

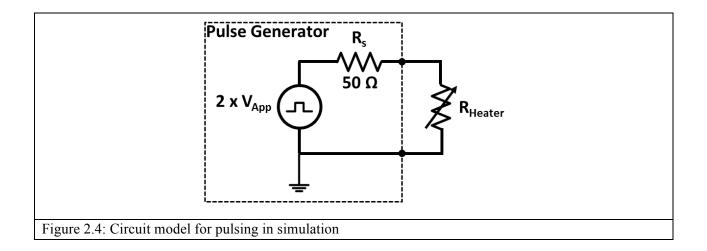

The material properties used for the model are shown in table 2.1. Because the fabricated devices are pulsed using a pulse generator with a 50  $\Omega$  source impedance, the same set up must be modeled using the electric circuits module (fig. 2.4). This is necessary to make the appropriate correction for the reflected voltage due to the heater resistance not matching the source impedance of the pulse generator during the entire duration of the pulse. The pulse generator output is twice the applied voltage ( $V_{App}$ ) with a 50  $\Omega$  source impedance in an attempt to deliver  $V_{App}$  to a 50  $\Omega$  load which, in this case, is the heater. However, the heater acts as a variable resistor and its resistance increases as it heats up. This results in an increasing voltage across the heater.

| Material                                            | Density<br>(kg/m <sup>3)</sup> | C <sub>p</sub><br>(J/kg-K) | k <sub>th</sub><br>(W/m-K)             | ٤ <sub>r</sub> | Resistivity<br>(Ω-m) | TCR   |  |  |

|-----------------------------------------------------|--------------------------------|----------------------------|----------------------------------------|----------------|----------------------|-------|--|--|

|                                                     |                                |                            |                                        | 8.9⊥c,         |                      |       |  |  |

|                                                     |                                |                            |                                        | 11.11  c       |                      |       |  |  |

| Sapphire                                            | 3965                           | fig. 2.3(b)                | fig. 2.3(a)                            | [55]           | $10^{6}$             | 0     |  |  |

|                                                     |                                |                            | $174 \times 7.2^{-8}$                  |                |                      |       |  |  |

| W                                                   | 19350                          | 132                        | $\overline{7.2^{-8}(1+.003(T-300))}$   | 1              | 7.20 <sup>-8</sup>   | 0.003 |  |  |

| AlN                                                 | 3260                           | 740                        | 50                                     | 9 [47]         | $10^{6}$             | 0     |  |  |

| x-GeTe                                              | 6140                           | 303                        | 1                                      | 18             | $1.68^{-6}$          | 0.004 |  |  |

| a-GeTe                                              | 6140                           | 303                        | 1                                      | 18             | 10                   | 0     |  |  |

|                                                     |                                |                            | $317 \times 3.42^{-8}$                 |                |                      |       |  |  |

| Au                                                  | 19300                          | 129                        | $\overline{3.42^{-8}(1+.0024(T-300))}$ | 1              | 3.42-8               | 0.002 |  |  |

| Cu                                                  | 8960                           | 384                        | 200                                    | 1              | 3.35-8               | 0.002 |  |  |

| $SiO_2$                                             | 2200                           | 730                        | 1                                      | 3.9            | $10^{6}$             | 0     |  |  |

| Table 2.1: Material properties for use in the model |                                |                            |                                        |                |                      |       |  |  |

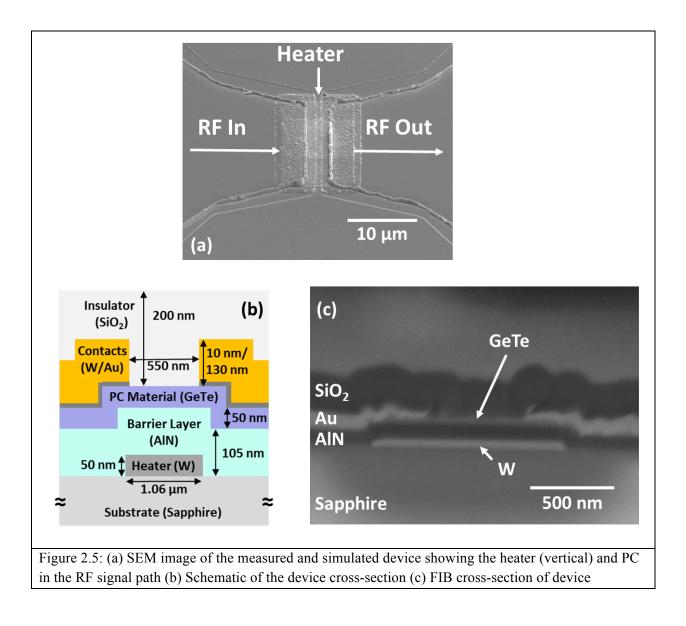

To check the validity of the model parameters, the results of experimental measurements on a fabricated switch (fig. 2.5) were compared to simulations. One hundred nanosecond long amorphization pulses with increasing  $V_{App}$  were applied across the heater (vertical structure in fig. 2.5(a)) while measuring the switch resistance between RF-In and RF-Out (fig. 2.5(a)). The schematic of the cross-section of the device (fig. 2.5(b)) shows the layer thicknesses, width of the heater and length of the RF gap measured from the FIB cross-section of the device (fig. 2.5(c)). The switch is 20 µm wide with a 550 nm long RF gap. The heater is 1.06 µm wide and 25 µm long with 105 nm of AlN between the heater and the GeTe.

#### 2.5 Simulations of 3D Model vs. Measurement Results

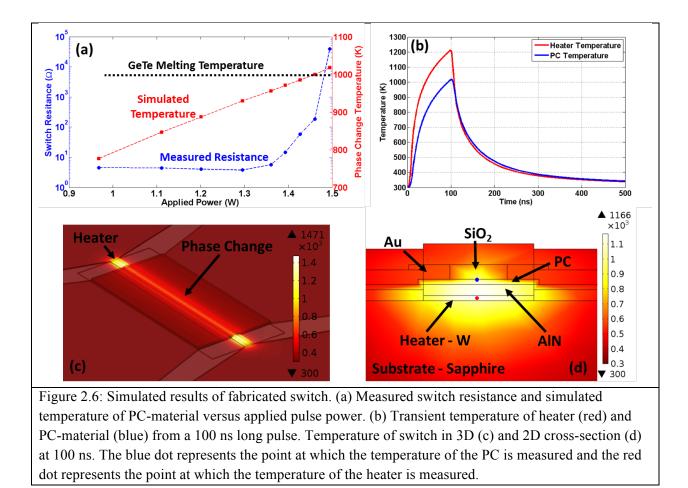

Fig 2.6(a) shows the measured switch resistance (blue) after subsequent 100 ns long pulses with increasing pulse power. When  $V_{App}$  reaches 8.7V (1.47 W applied pulse power), the resistance of the switch is 50 k $\Omega$  and is considered "off". The simulated temperature (red) at the top of the GeTe in the RF gap increases with applied pulse power and crosses over the melting temperature of the GeTe (996 K [39]) at 1.47 W, resulting in the amorphization of the GeTe. This shows that the measured minimum power to amorphize (MPA) the switch occurs when the top of the GeTe gets slightly above the melting temperature. The 1.47 W is the initial applied power based on the  $V_{App}$  and the resistance of the switch at

room temperature. The heater resistance is 39.9  $\Omega$  at room temperature but, as the temperature of the heater rises, the resistance increases to 120  $\Omega$ . Therefore, the power being delivered to the heater is decreasing once its resistance is above 50  $\Omega$ .

Fig 2.6(b) shows the simulated temperature transient of the MPA pulse for the middle of the heater (red) and the top PC-material (blue) from a 100 ns long pulse. The PC gets slightly above 1000 K by the end of the pulse, while the heater gets slightly above 1200 K. The time it takes for the PC to move from the melting temperature (996 K) to the crystallization temperature (200 K [29]) is less than 100 ns and is fast enough to amorphize the GeTe. The temperature of the switch at 100 ns for the MPA pulse is shown in 3D (fig. 2.6(c)) and 2D cross section (fig. 2.6(d)). Fig. 2.6(c) shows that the maximum temperature of the switch is actually at both ends of the heater where neither PC nor Au is present. The

2D cross-section (2.6(d)) shows the locations where the heater (red point) and PC (blue) temperatures are measured. It should be noted that there is almost zero temperature gradient across the thickness of the AlN barrier layer and that almost all of the temperature difference between the heater and the top of the PC is in the PC layer.

#### 2.6 3D Model vs. 2D Model

Full 3D simulations are time consuming (> 1 hour per transient simulation) and require a significant amount of computing power. For the rest of the simulations in this chapter, 2D models using a cross-section of the device will be simulated (< 5 minutes per transient simulation). Because it is a 2D model, only the heat transfer physics can be used. The heater is set as the heat source in the simulation. The power,  $P_H$ , dissipated in the heater is a function of the voltage across the heater and the temperature dependent heater resistance (as shown in *eq 2.2*), where  $V_{App}$  is the voltage from the pulse generator and  $\Gamma$  is the reflection coefficient due to the mismatch between the source and load ( $R_H$ ) impedance.  $R_H$  is the temperature dependent resistance of the heater (as shown in *eq 2.3*).

$$P_{H} = \frac{(V_{App}(1+\Gamma))^{2}}{R_{H}}$$

(2.2)

$$R_H = R_{H0}(1 + \alpha(\bar{T} - 300)) \tag{2.3}$$

$R_{H0}$  is the initial resistance of the heater based on its width, length (25 μm), thickness (50 nm) and the resistivity of the W.  $\overline{T}$  is the average temperature of the heater in kelvin and α is the measured TCR of W.  $R_H$  is also used to calculate  $\Gamma$  (as shown in eq. 2.4).  $R_S$  is the source impedance of the pulse generator (50 Ω) and  $R_{HC}$  is the resistance of the heater leads and is estimated to be 6 Ω. The average temperature of heater,  $\overline{T}$ , is used to calculate the  $R_H$ , because this is the only way it can be implemented in the model. Calculating the average resistance of the heater based on the temperature at each point in the heater is not possible using a 2D model. The uses of  $\overline{T}$  is shown to be an adequate approximation due to its match to the 3D model.

$$\Gamma = \frac{R_H - (R_S + R_{HC})}{R_H + R_S + R_{HC}} \tag{2.4}$$

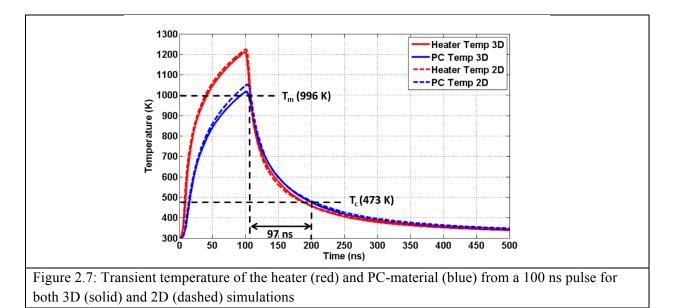

A 2D model of the switch in fig 2.5 was simulated with the same  $V_{App}$  of 8.7 V for a 100 ns long pulse and compared to the 3D simulation (fig. 2.7). The heater reaches nearly the same temperature (center point) for both the 3D and 2D simulations while the PC temperature is about 30 K higher in 2D than in 3D. This difference is most likely a result of the out of plane heat flow that is missing in the 2D simulation. The cooling times for both simulations are identical and the 2D simulation is accurate enough to be used for the remaining simulations in this chapter. The following simulations are intended to demonstrate the effects of adjusting the following variables: RF gap length, heater width, barrier layer thickness, use of a notch in the PC-material and amorphization pulse length. They are not intended to predict the outcome of a specific fabricated switch.

#### 2.7 Simulation Results of Design Parameter Sweep

#### 2.7.1 RF Gap Length

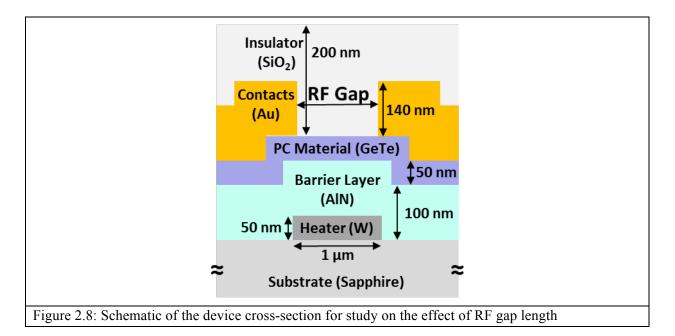

The RF gap is the distance between the two electrodes on top of the PC-material (fig 2.8). As previously discussed, the length of this gap most directly contributes to the ON-state resistance of the switch. However, the top electrodes are made from Au and are thermally conductive, thereby creating a shunt path to thermal ground. This shunt path becomes smaller as the RF gap shrinks, making it difficult to melt the PC-material in the gap. A 2D model (fig. 2.8) was simulated while changing the RF gap length from 100 nm to 900 nm long using 100 nm increments. The MPA was found by increasing applied pulse power until the top of the PC-material in the RF gap reached the melting temperature (996 K) by the end of a 100 ns long amorphization pulse.

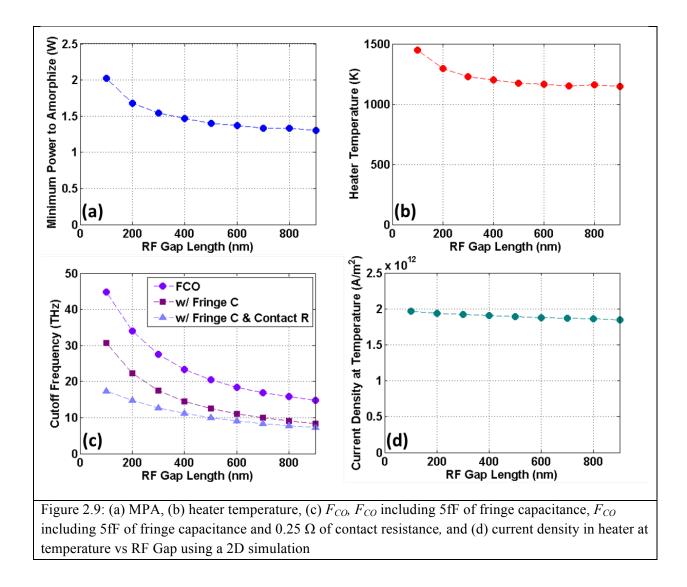

As expected, the MPA of the device decreases with increasing RF gap length (fig. 2.9(a)). However, the trend is not linear. Increasing the length past 500 nm does not decrease the MPA significantly. The temperature of the heater at the end of the 100 ns long MPA pulse (fig. 2.9(b)) also decreases as the RF gap length increases and flattens out at about 1200 K. These two results show that when the RF gap is small, the top electrodes create larger thermal gradients in the PC-material thereby requiring more power to be generated in the heater to melt the top of the PC-material. However, there will always be a 200 K difference between the heater temperature and the top of the PC because of the thermal gradients present in PC layer.

The  $F_{CO}$  (fig. 2.9(c)(circles)) decreases with increasing gap length due to the increase in ON-state resistance ( $R_{ON}$ ). The OFF-state capacitance ( $C_{OFF}$ ) decreases slightly with increasing gap length, but the increase in  $R_{ON}$  dominates the  $F_{CO}$ . The 2D-simulation does not take into account any fringing capacitance that may be present between the pads. When 5 fF of fringing capacitance is added (squares), the  $F_{CO}$  decreases by over 14 THz for a 100 nm gap. When 0.25  $\Omega$  of contact resistance is also included with the fringing capacitance (triangles), the  $F_{CO}$  decreases even more dramatically at shorter RF gaps. These assumptions for fringing capacitance and contact resistances are based on measured results from fabricated devices and will be discussed in the later chapters.

The current density in the heater at 100 ns from the MPA pulse (fig. 2.9(c)) is not significantly affected by RF gap length and reduces by less than 10% when gap length is increased from 100 nm to 900 nm. Minimizing the heater temperature and current density can prolong the lifetime of the heater if electromigration is one of the heater's failure mechanisms [56].

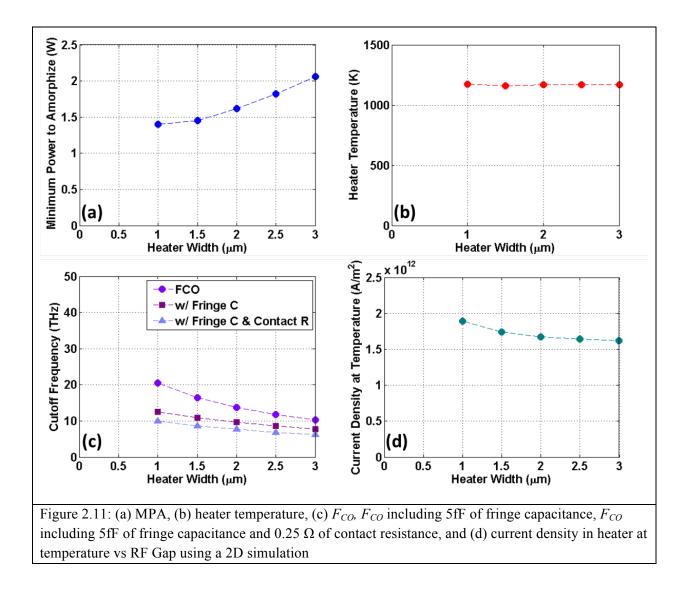

#### 2.7.2 Heater Width

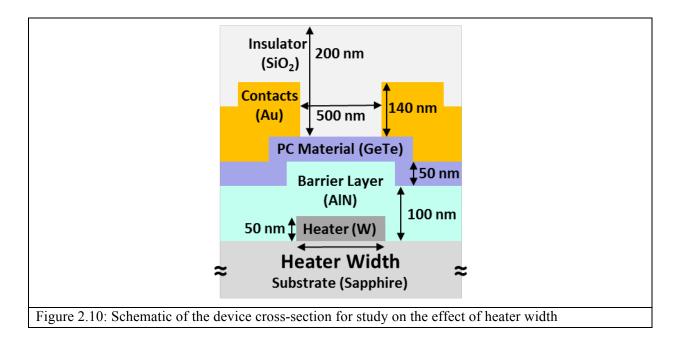

A 2D model was built to simulate the effect of changes in heater width (fig 2.10) while the RF gap length was held constant at 500 nm. A 50 nm thick heater was used on a sapphire substrate with a 100 nm thick AlN barrier layer and 50 nm of GeTe. The MPA (fig. 2.11(a)) increased with heater width. Due to the increase in contact area between the heater and substrate, an increase in power is needed to reach the target temperature because the thermal resistance to ground decreased. As expected, the temperature of the heater remains constant at MPA (fig. 2.11(b)) and, therefore, no additional thermal

gradients are present in the PC-material due to an increase in heater width. The results in fig 2.11(a) suggest that even heaters with sub-micron widths would still require 1.4 W to amorphize the PC-material. The MPA increases at 0.45 W per micron of heater width.

The  $F_{CO}$  decreases with increasing heater width (fig. 2.11(c)) from 20 THz at 1 µm to 10 THz at 3 µm. The decrease in  $F_{CO}$  is a result of increasing  $C_{OFF}$  as  $R_{ON}$  remains constant with changes in heater width. The increase in  $C_{TH}$  (fig. 2.2) is due to the increase in overlap area between the heater and the top electrode. As expected, the  $F_{CO}$  with 5 fF of fringe capacitance and 0.25  $\Omega$  of contact resistance becomes less dependent on heater width.

The current density in the heater at temperature decreases with heater width (fig. 2.11(d)); however, after 2  $\mu$ m the decrease is not significant. Increasing the heater width does not improve performance in any way. The only reason to increase the width of the heater is to reduce the current density if the durability of the heater is in question. However, there are more efficient ways to improve the heater durability than by making the heater wider, such as using switches in parallel to make the heater shorter in length.

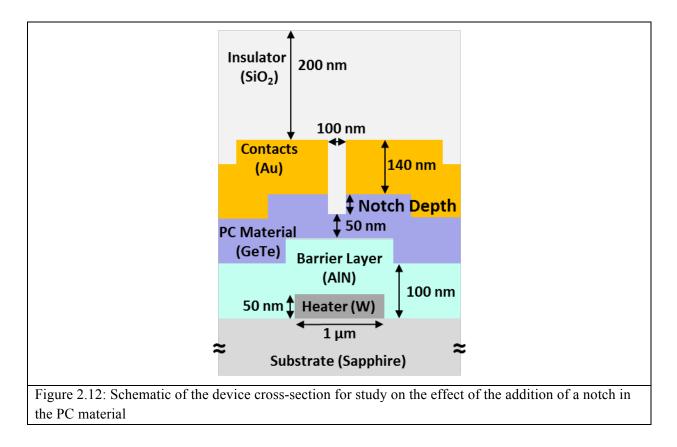

#### 2.7.3 Notch Design

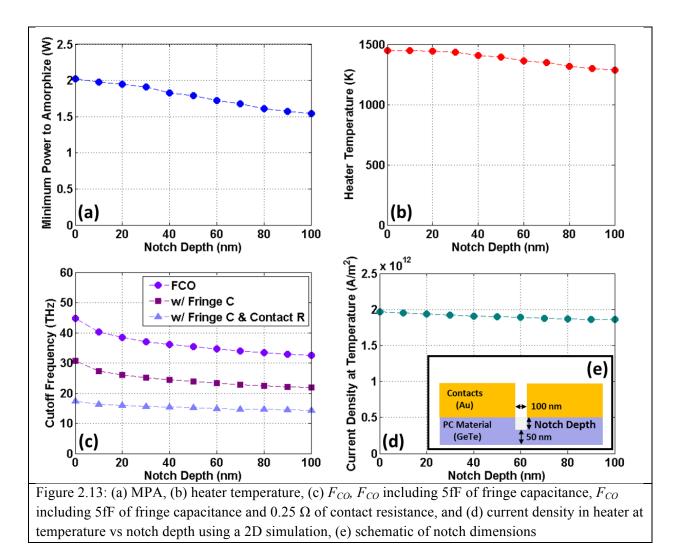

Without considering the effects of fringing capacitance and contact resistance, the highest performing simulated switch has  $F_{CO}$  of 45 THz and has a 1 µm wide heater with a 100 nm long RF gap. However, it has the highest MPA and requires over 2 W to melt the PC-material. The smallest RF gap also requires the heater to reach a temperature of almost 1500 K. In an effort to reduce the MPA, a notch can be made into the PC layer to limit the effect of the electrodes on shunting the heat flow. The notch is created by having a thicker PC layer and patterning the RF gap into the PC until it is 50 nm thick (fig. 2.12). The extra PC-material has a thermal conductivity of 1 W/m-K while still being electrically

conductive, which thereby allows the increased thermal gradients caused by the electrodes to be reduced in the PC-material under the notch. This reduces the MPA (fig 2.13(a)) and the temperature the heater (fig 2.13(b)) must achieve to melt the PC-material. As the notch depth increases, the MPA reduces from 2 W down to 1.5 W.

The  $F_{CO}$  also decreases with increasing notch depth (fig 2.13(c)). R<sub>ON</sub> increases because the current flows through on-state PC material down to the notch, which results in the  $F_{CO}$  decreasing from 45 THz down to 32 THz. The decrease in  $F_{CO}$  is larger than the reduction in MPA, thus making the trade-off seemingly unnecessary. However, the addition of any fringing capacitance or contact resistance results in the  $F_{CO}$  being less affected by notch depth. This results in the notch having some benefit. The MPA decreases by 25% while the FCO with 5 fF of fringe capacitance and 0.25  $\Omega$  of contact resistance only reduces by 10%.

The current density in the heater decreases with increasing notch depth (fig 2.13(c)). However, this decrease is minimal and, even at a notch depth of 100 nm, is only reduced by less then 10%. The higher current density along with the higher heater temperature may reduce heater reliability and must be considered if heater durability is in question.

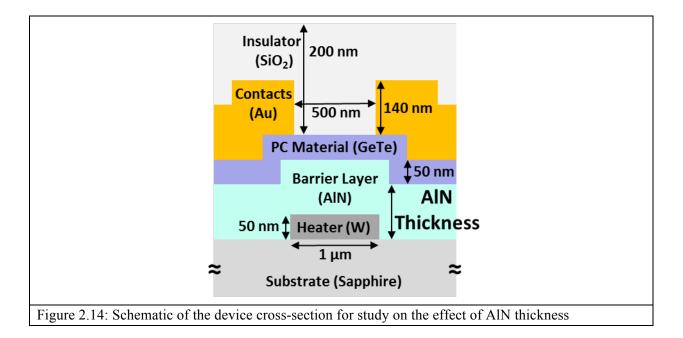

#### 2.7.4 Barrier Layer Thickness

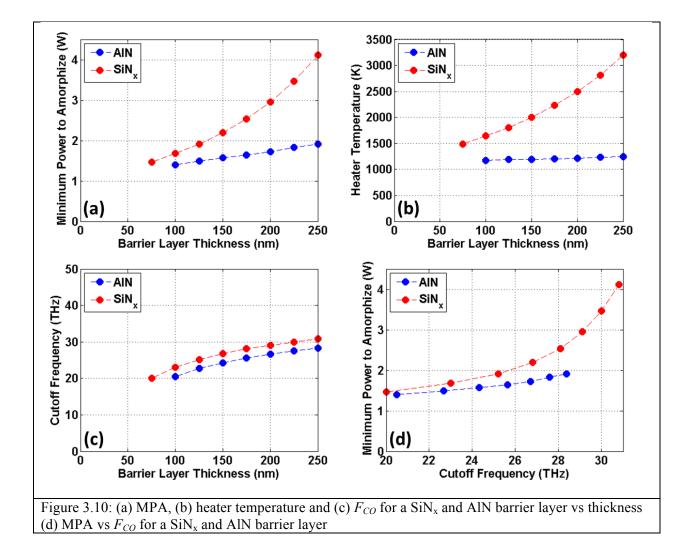

As previously discussed, the barrier layer between the heater and PC-material plays an important role in the performance of the switch. The barrier layer is needed to electrically isolate the RF signal path from the programming path while thermally connecting the heater to the PC material. AlN was chosen as the material for the barrier layer because it is thermally conductive while still being an electrical insulator. To further isolate the heater from the RF signal path, the barrier layer thickness can be increased. However, increasing the thickness of the barrier layer does have its consequences. A 2D model was simulated (fig. 2.14) to determine the effect of increasing the thickness of the AlN. The heater width and RF gap length remained constant at 1 µm and 500 nm, respectively.

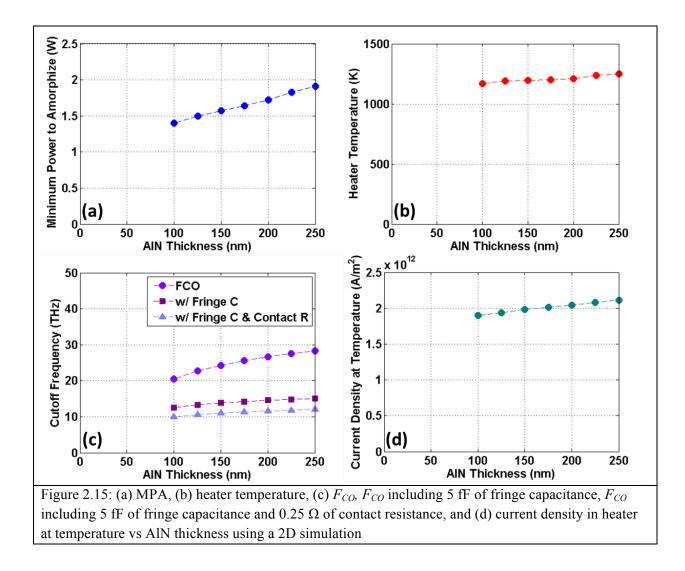

As expected, the MPA increased with increasing AlN thickness (fig. 2.15(a)). However, not all of the increase in the power required to melt the top of the PC-material can be attributed to the additional thermal resistance between the heater and PC-material. The additional heat capacitance also contributes to the increase in MPA. The total volume that must be heated increases with thicker AlN layers, thereby increasing the thermal heat capacitance. Because MPA pulses are only 100 ns long, the increase in heat

capacitance reduces the speed at which the volume surrounding the heater increases in temperature. To overcome this, more power is needed to address the increase in heat capacitance. By using AlN as the barrier layer instead of  $SiN_x$  or  $SiO_2$ , the increase in MPA resulting from increased barrier layer thickness is reduced. The MPA only increases by 1/3 W per 100 nm of additional AlN.

The heater temperature increases slightly with increasing AlN thickness (fig. 2.15(b)), but the difference in temperature between the heater and the top of the PC-material only increases from 200 K to 250 K. This small increase further supports the claim that the rise in MPA is due mostly to the increase in heat capacity and not to the thermal resistance from the additional AlN thickness.

The  $F_{CO}$  increases with AlN thickness (fig. 2.15(c)) from 20 THz to 28 THz due to the reduction in  $C_{OFF}$ . An increase of almost 50% in  $F_{CO}$  resulted in only a 33% increase in MPA. However, the reduction in  $C_{OFF}$  due to increasing the AlN thickness begins to saturate after 250 nm, resulting in a maximum  $F_{CO}$  of 35 THz. Therefore, increasing the thickness of AlN past a certain point affects the MPA more than the  $F_{CO}$ . The maximum  $F_{CO}$ /MPA ratio occurs at 175 nm of AlN, making it the optimal thickness for the barrier layer. The addition of fringing capacitance and contact resistance diminishes the advantage of increasing the thickness of AlN. The gain in  $F_{CO}$  drops from 50% down to 20%, thus making it lower than the increase in MPA. Therefore, 100 nm of AlN is the ideal thickness for the barrier layer.

The current density in the heater increases slightly with increasing AlN thickness (fig. 2.15(b)). The increase in current density corresponds to the increase in MPA. However, the current density only increases by 10%. If the durability of the heater is in question, then this increase in current density may limit the thickness of the barrier layer that can be used in the switch.

#### 2.7.5 The Effect of Pulse Length on MPA

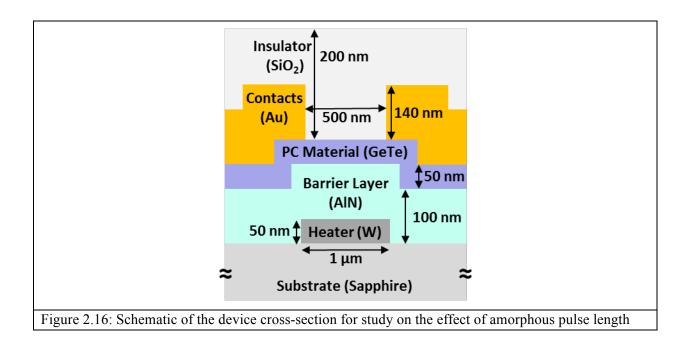

The length of the amorphization pulse is not fixed. For the previous simulations, it was held constant at 100 ns in duration; however, increasing the length of the pulse can reduce the voltage required

to amorphize the switch [16] as well as the MPA. A 2D model of a standard switch (fig. 2.16) with a 1  $\mu$ m wide heater, 100 nm of AlN and a 500 nm long RF gap is simulated using different amorphization pulse lengths ranging from 50 ns to 1  $\mu$ s.

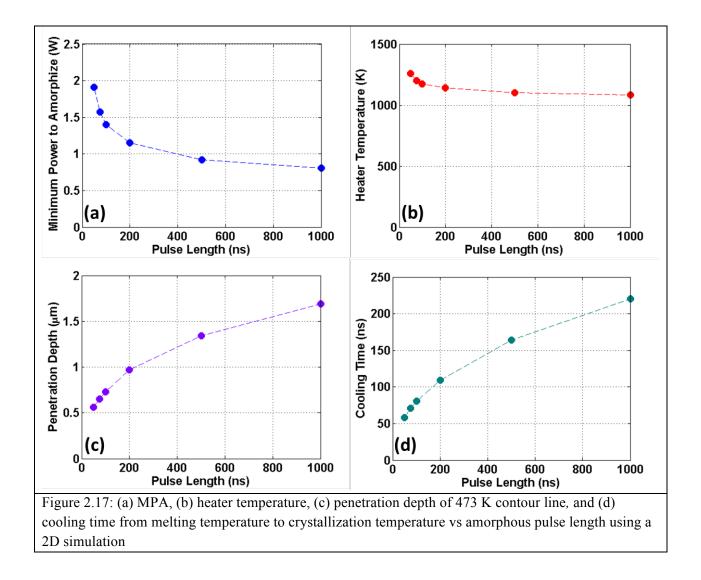

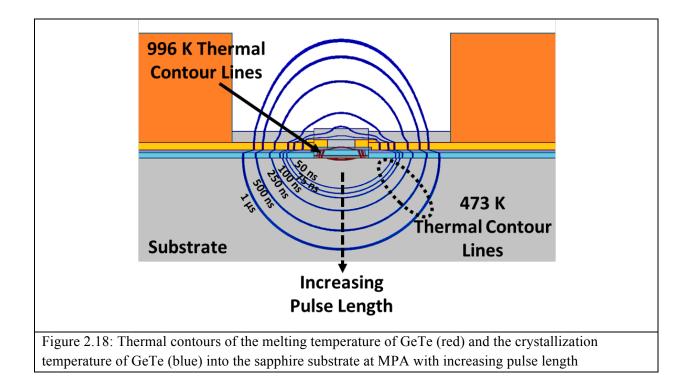

As the pulse length increases, the MPA decreases (fig. 2.17(a)) significantly down to 0.8 W for a 1 µs long pulse. However, going beyond that pulse length does not result in a significant reduction in MPA. The heater temperature also decreases as a result of longer pulses (fig. 2.17(b)). The reduction in MPA and heater temperature is due to the heat capacity of the system becoming less of a determinant for longer pulses. However, increasing the pulse length does lead to an increased volume in the device being heated. Fig. 2.17(c) shows the how deep the 473 K (crystallization temperature) contour line goes into the sapphire substrate. As the pulse width increases, the penetration depth into the substrate gets longer and does not plateau. This increase in penetration depth and heated volume leads to an increase in cooling time of the PC-material at the top of the switch (fig. 2.17(d)) which could lead to the inability to quench the molten PC-material quickly enough for it to become amorphous. If the crystallization time is shorter then cooling time, the switch will never be able to turn off. Therefore, the MPA can only be reduced up to a certain point.

Fig. 2.18: shows the thermal contours for 996 K (red) and 473 K (blue) at the end of the MPA pulse for each pulse length. The area inside the red contour lines is hot enough to melt the PC-material and needs to be cooled below the crystallization temperature (473 K). The area inside the blue contour lines is above the crystallization temperature and represents the increased volume into the substrate that must be cooled. This suggests that if the crystallization time of the PC-material is faster than the cooling time, a shorter pulse with more power may be used to turn the switch off if longer pulses cannot do so. Crystallization times of less than 150 ns are assumed to be fast enough for this work.

#### 2.8 Summary

There are many factors to consider when designing, modeling and simulating a 4-terminal inline RF phase change switch. The choice of PC-material and material for the barrier layer is critical for maximizing the performance of the switch. In this work, GeTe was chosen as the PC-material because of its low resistivity in the ON-state (1.68  $\mu$ Ω-m) and AlN was chosen for the barrier layer due to its high thermal conductivity (285 W/m-K) as compared to other dielectrics such as SiN<sub>x</sub>.

Including the temperature dependence of sapphire's thermal conductivity and heat capacity as well as a thermal interface between the W heater and sapphire substrate was necessary to ensure the model's accuracy. The use of 2D models could be substituted for larger 3D models to save on computing power without sacrificing simulation accuracy. The heat of fusion of GeTe was not included in the simulation results due to its difficulty to implement in the model. The heat of fusion increases the required energy to melt the GeTe and as a result the simulated MPAs reported underestimates the actual power required to amorphize the GeTe. However, the volume of GeTe that is melted only accounts for

10% of the total heated volume, and thus the heat of fusion will only increase the simulated MPA by 10%.

When designing a 4-terminal inline RF phase change switch, there are three main design points that must be considered. RF gap length, the use of a notch and the thickness of the AlN barrier layer all trade off power for increased performance. Minimizing the heater width not only improves performance but also reduces power consumption. Therefore, using the narrowest heater is ideal unless it reduces heater reliability. If there is not any limitation on power, a switch with a short RF gap and thick AlN layer would yield the best performance. Even when considering power, an RF gap of 100 nm has the highest  $F_{CO}$ /MPA ratio for all the devices simulated. When 5 fF of fringe capacitance is added, a 100 nm RF gap still has the highest  $F_{CO}$ /MPA ratio. However, when 0.25  $\Omega$  of contact resistance is also included, the use of a 100 nm deep notch with a 100 nm RF gap results in the highest  $F_{CO}$ /MPA ratio. All of these conclusions are based upon a 20  $\mu$ m wide switch and would vary slightly for switches of different widths. While contact resistance would scale with the switch width, the fringe capacitance would not.

The advantage of a notch is apparent for situations in which there is fringing capacitance and contact resistance. However, in the other cases it may seem to add unnecessary complexity. If the design was limited by having only 1.6 W of available power, a switch with either 300 nm long RF gap with no notch or one with a 100 nm long RF gap and 100 nm notch could be used. The switch with a 300 nm RF gap would have an  $F_{CO}$  of 27.5 THz, while the switch with the notch would have an  $F_{CO}$  of 32.5 THz. Even with the addition of fringing capacitance and contact resistance, the switch with the notch would always have a higher  $F_{CO}$ . Therefore, the use of a notch can reduce power without sacrificing as much performance as would be incurred by increasing the RF gap length.

## Chapter 3: Phase Change RF Switch Fabrication

## 3.1 Abstract

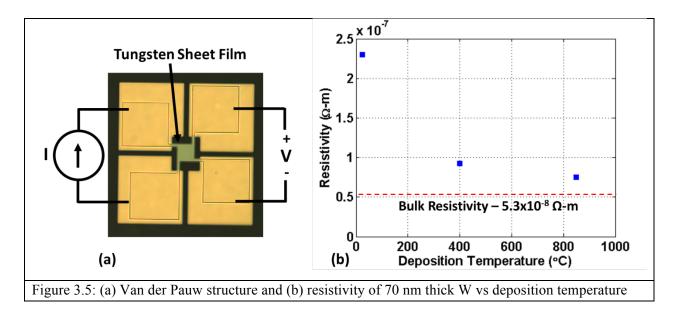

Manipulating the device design is important in maximizing switch performance, but it can only go so far. Improving the materials used in the switch allows for additional improvements in performance that cannot be achieved by just reducing the RF gap length or heater width. In this chapter, three major contributions to the materials used in the switch are detailed. The introduction of a low resistivity W heater (75 nΩ-m), high-thermal conductivity barrier layer (~50 W/m-K) and lowest demonstrated GeTe resistivity (1.5  $\mu$ Ω-m) result in the *F<sub>co</sub>*/MPA ratio doubling from 7.8 THz/W to 15.6 THz/W when compared to the materials used in the current state-of-the-art PC switch [15].

#### 3.2 Introduction

Improving the electrical and thermal properties of the switch are important to further increase its performance. The current state-of the-art RF PC switch [15] uses a high resistivity NiCrSi heater (1500 n $\Omega$ -m), low thermal conductivity SiN<sub>x</sub> barrier layer (~1 W/m-K) and has a GeTe resistivity of 3.6  $\mu\Omega$ -m. Reducing the GeTe resistivity has the most direct impact on RF performance. The use of a higher thermal conductivity barrier layer such as AlN would allow for a reduction in MPA while reducing OFF-state capacitance. Changing the heater material used from NiCrSi to W allows for reduction in actuation voltage due to a reduction in resistivity.

This chapter will discuss the fabrication process of a standard 4-terminal inline RF phase change switch as well as one with a notch. In addition, three major advancements in materials used over prior works will also be discussed: W heaters, an AlN barrier layer and low resistivity GeTe.

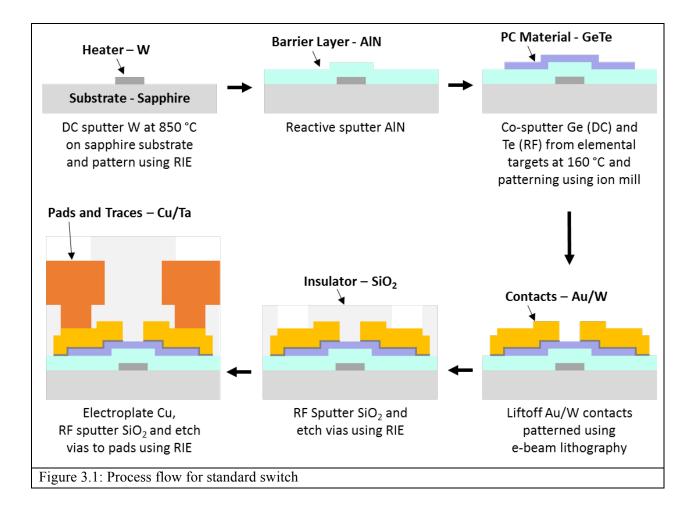

#### 3.3 Standard Switch Process Flow

Fig. 3.1 shows the process flow for a standard switch. As discussed in the previous chapter, the switch is built on a sapphire substrate. To prepare it for the first layer, the sapphire substrate it is placed in a beaker of acetone and sonicated for 10 minutes. It is then rinsed with acetone and isopropyl alcohol (IPA). The substrate is cleaned in the  $O_2$  plasma asher for 1 minute to remove any organic residue that might remain.

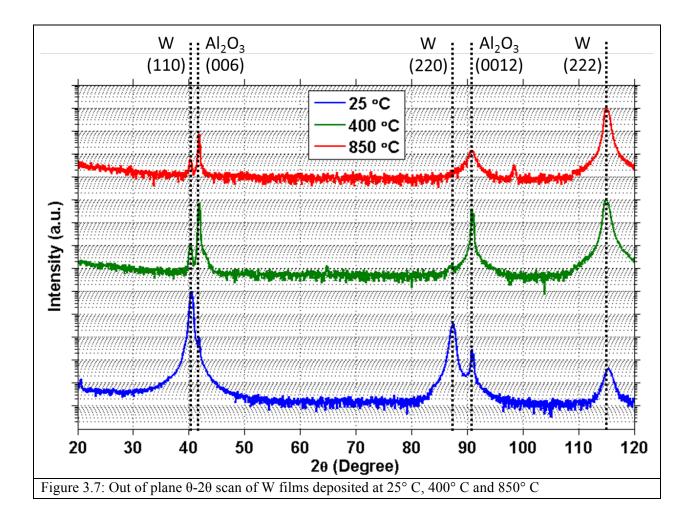

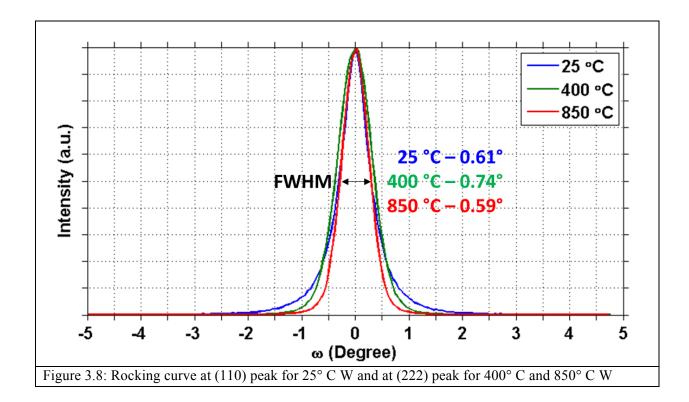

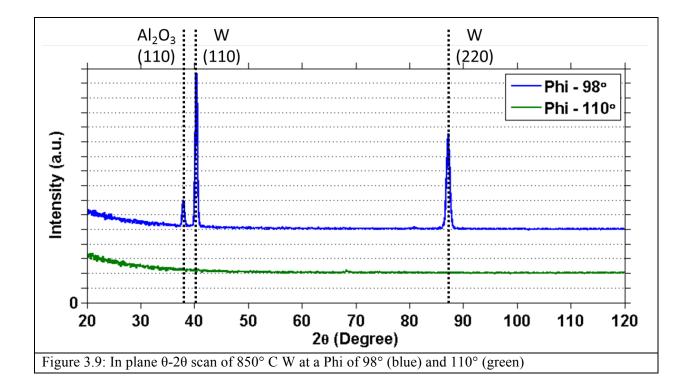

The sapphire substrate is then heated and maintained at 850° C while W is deposited using DC magnetron sputtering for 1800 seconds yielding approximately 70 nm of W. Once the deposition is complete, the substrate is allowed to cool to about 40 °C inside the vacuum chamber. The sample is then patterned using 1 µm of photoresist. It is necessary to use a 10 minute Hexamethyldisilazane (HMDS)

vapor prime on the sample prior to spin coating it with photoresist. The HMDS vapor prime is required for the photoresist to adhere to the W film and prevent alignment marks from washing away during development. The W is etched using a  $CHF_3$  and  $O_2$  gas chemistry in a parallel plate reactive ion etcher (RIE). The photoresist is removed by a thorough cleaning in the  $O_2$  plasma asher for 3 minutes followed by a 10 minute sonication in acetone. This process ensures that no photoresist residue remains on the heaters.

After the heaters are patterned, the next step is to deposit the 100-200 nm thick AIN barrier layer. The surface of the sample is first cleaned using a 1 minute sputtered etch. Then AIN is reactively sputtered from Al targets in a nitrogen rich environment using an S-Gun configuration [57]. Two doughnut shaped Al targets sputtered using AC magnetron sputtering (40 kHz) are used to prevent the disappearing anode effect that is present in DC reactive sputtering. The sputtering environment is N<sub>2</sub> rich which causes "poisoning" of the Al target where the AlN is being formed on its surface and then sputtered off onto the substrate. As a result of this sputtering process, polycrystalline AlN is deposited on the sample.

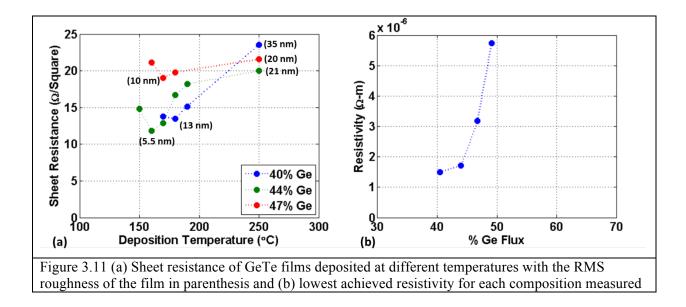

After the deposition of the AlN barrier layer, a 50-100 nm thick phase change layer is deposited. The PC-material is co-sputtered from elemental Ge and Te targets. The Ge uses DC magnetron sputtering while the Te uses RF magnetron sputtering. RF magnetron sputtering is used for Te to reduce the sputtering rate to one similar to that of Ge. The sputtering conditions used are critical in minimizing the resistivity of the GeTe and will be discussed later in the chapter. Before the deposition takes place, the substrate is heated to 160° C. A 1 minute sputter etch is performed to clean the surface of the sample. After the sputter etch is completed, the GeTe is then deposited. The sample remains in the vacuum chamber to cool down before it is removed. The deposition temperature of 160° C was experimentally determined and will be discussed in further detail later in the chapter. A 1 µm thick photoresist layer is used to pattern the GeTe. The photoresist also has difficulty adhering to the GeTe and, therefore, a 10 minute HMDS vapor prime is required before the sample is coated the photoresist. The GeTe is etched using an  $Ar^+$  ion mill. After ion milling, the surface of the photoresist becomes hard and is difficult to remove. Therefore, it is necessary to first to thoroughly clean it in the O<sub>2</sub> plasma asher for 3 minutes followed by a 10 minute sonication in acetone to remove the photoresist.

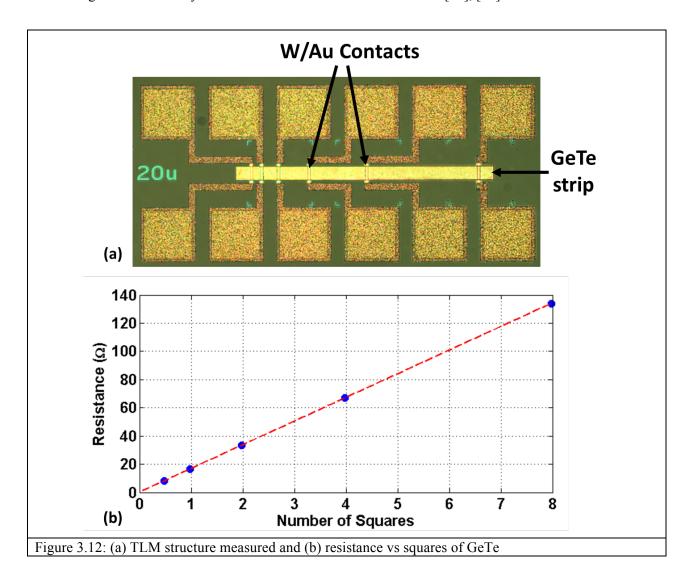

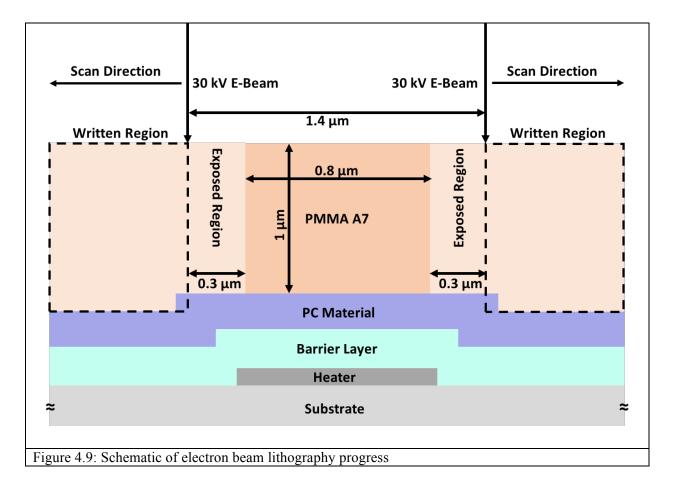

Once the GeTe is patterned, the Au contacts are created using a lift-off process. This layer uses electron beam lithography to pattern the area where Au contacts are to be deposited. A 1  $\mu$ m thick PMMA A7 ebeam-resist is spin coated onto the sample. Because the sapphire substrate is electrically insulating, a thin 10 nm layer of A1 is deposited on top of the resist to minimize charging. The patterns are written using a 30 kV beam voltage with a beam current between 25-30 pA. The resist is exposed with a dose of 300  $\mu$ C/cm<sup>2</sup>. After the exposure of all of the devices is completed, the A1 layer on top of the resist is removed by dipping the sample in diluted AZ400K developer solution for 30 seconds. Once the A1 layer is removed, the resist can be developed using a 1:3 MIBK/IPA solution for 1 minute followed by a dip in IPA for 15 seconds. Next, a low power 2 minute descum in the O<sub>2</sub> plasma asher is conducted to remove any residual ebeam resist that maybe present in the contact windows. The sample is then placed in the vacuum chamber where the sample surface is sputter etched for 3 minutes before the metallization is deposited. After the sputter etch, 10 nm of W is deposited using DC magnetron sputtering. Once the deposition is completed, the sample is the sonicated in acetone for 10 minutes or until all of the W/Au metal is lifted off.

The next step is to deposit a 100 nm thick protective  $SiO_2$  layer over the entire sample. This layer is needed to protect the GeTe in the RF gap from being etched when the Cu seed layer is removed after electroplating the pads and traces. The SiO<sub>2</sub> layer is deposited using RF magnetron sputtering. A 1  $\mu$ m thick photoresist is spun onto the sample and the vias are exposed over the Au contacts. Vias in the SiO<sub>2</sub> are etched using a CHF<sub>3</sub> and O<sub>2</sub> gas chemistry in a parallel plate RIE. The photoresist is then removed.

In order to make electrical contact to the heater pads, vias are etched into the AlN barrier layer. A 1 µm thick photoresist is spun onto the sample and the vias are exposed over the W heater pads. The AlN is etched using an inductively coupled plasma (ICP) RIE. The gas chemistry used for the etch is 25% Cl<sub>2</sub>, 5% BCl<sub>3</sub> and 70% Ar. After the etch is completed, the photoresist is removed using a thorough clean in the O<sub>2</sub> plasma asher for 3 minutes followed by a 10 minute sonication in acetone.

After the vias are etched in the SiO<sub>2</sub> and AlN, the seed layer for electroplating the pads and traces is deposited. First, the sample is sputter etched for 5 minutes to ensure good electrical contact to the Au. Then, 10 nm of Ta followed by 100 nm of Cu are deposited using DC magnetron sputtering. Next, 2  $\mu$ m of photoresist is spun onto the sample and the pads and traces are exposed. A low power 2 minute descum in the O<sub>2</sub> plasma asher is used to remove any residual photoresist that maybe present on the exposed Cu seed layer. The sample is then placed in a Cu electroplating bath. Using a pulsed power supply, with 15 ms of forward current and 1 ms of reverse current per pulse, for 20 minutes results in 2  $\mu$ m of plated Cu. Once the plating is completed, the photoresist is stripped and the Cu/Ta seed layer is removed using an Ar<sup>+</sup> ion mill.

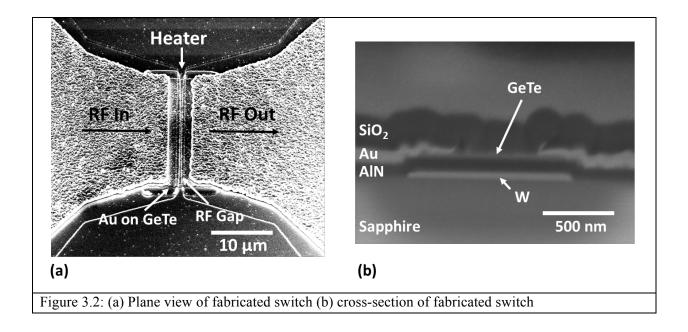

The next step is to deposit a 100 nm thick SiO<sub>2</sub> protective layer over the sample using RF magnetron sputtering. A 1  $\mu$ m thick photoresist is spun onto the sample and the vias are exposed over the plated Cu pads. Vias in the SiO<sub>2</sub> are etched using a CHF<sub>3</sub> and O<sub>2</sub> gas chemistry in a parallel plate (RIE) and the photoresist is then removed. A finished device and its cross-section are shown in fig. 3.2. A W heater runs vertically in fig. 3.2(a) directly on the sapphire substrate (fig. 3.2(b)). A 100 nm thick AlN barrier layer separates the W heater and GeTe (fig. 3.2(b)). The RF gap (fig. 3.2(a)) is defined by the space between the Au contacts onto of the GeTe as seen in fig. 3.2(b).

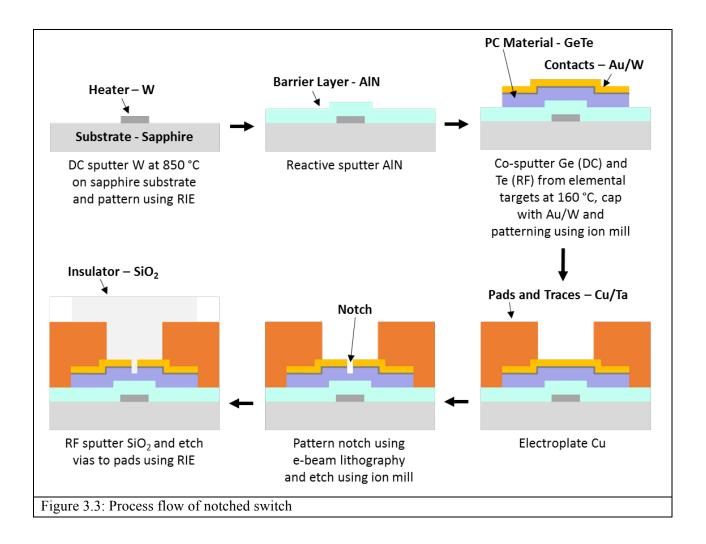

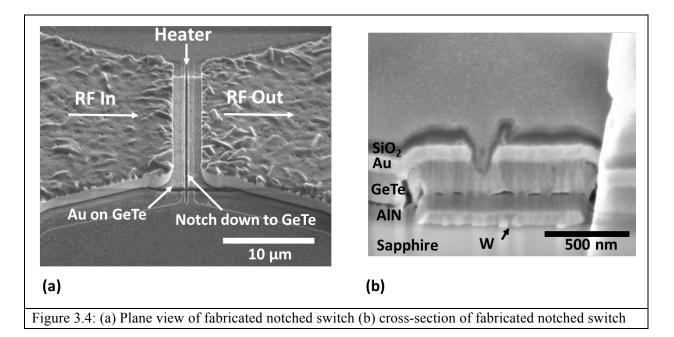

#### 3.4 Notched Switch Process Flow

The initial steps of the process flow for fabricating a 4-terminal inline RF phase change switch with a notch are the same as those for the standard switch for the heater and barrier layers (fig. 3.3). The patterning of the RF gap and notch are the last steps in the process. The sapphire substrate is cleaned and prepared in the same way as the standard switch. A 70 nm W film is deposited at 850 °C and the heaters are patterned using a CHF<sub>3</sub> and O<sub>2</sub> gas chemistry in the RIE. Next, the sample is sputter etched for 1 minute before 100-200 nm of AlN is deposited on the sample.

After the AlN barrier layer is deposited, a film stack of GeTe, W and Au is deposited without the sample breaking vacuum. This is done by first heating the substrate to 160 °C and cleaning the sample surface with a 1 minute sputter etch. After the sputter etch, 150 nm of GeTe is sputtered using the same co-sputtering technique as discussed earlier followed by 10 nm of W and 130 nm of Au. By depositing the entire stack without the sample breaking vacuum, a pristine interface is present between the GeTe layer and contact metal. This helps minimize any contact resistance ( $R_{PC}$ ) at this interface due to contamination. The whole stack is patterned by spin coating 1 µm of photoresist and etching it in an Ar<sup>+</sup> ion mill. The photoresist is removed using a thorough clean in the O<sub>2</sub> plasma asher for 3 minutes followed by a 10 minute sonication in acetone to ensure no photoresist residue remains.

Once the film stack is patterned and etched, the vias in the AlN barrier layer also must be etched in order to make electrical contact to the heater pads. A 1  $\mu$ m thick photoresist is spun onto the sample and the vias are exposed over the W heater pads. The AlN is etched using same ICP RIE recipe used in the standard switch. The photoresist is removed using a thorough clean in the O<sub>2</sub> plasma asher for 3 minutes followed by a 10 minute sonication in acetone.

After the vias in the AlN are made, the surface of the sample is sputter etched for 5 minutes before the Ta/Cu seed layer is deposited. The traces and pads are patterned using 2  $\mu$ m of photoresist

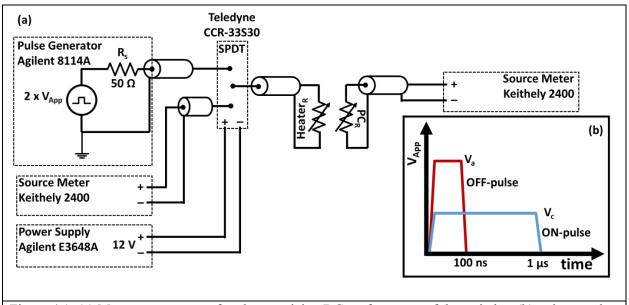

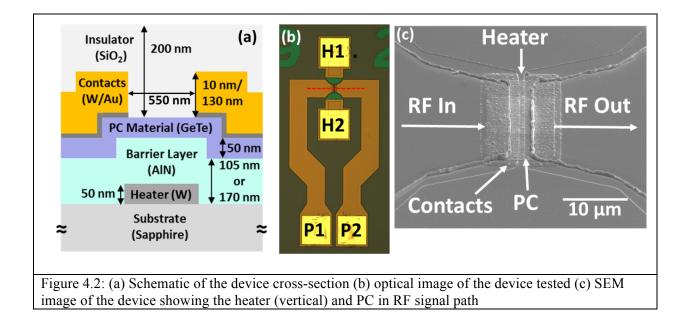

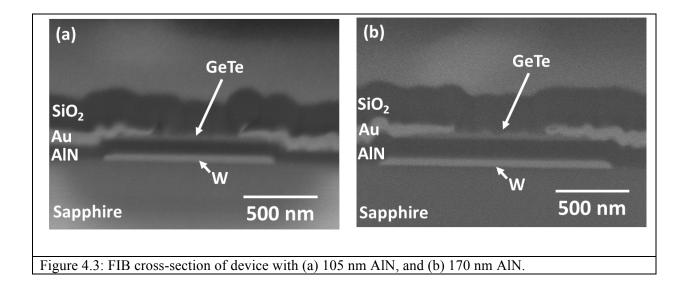

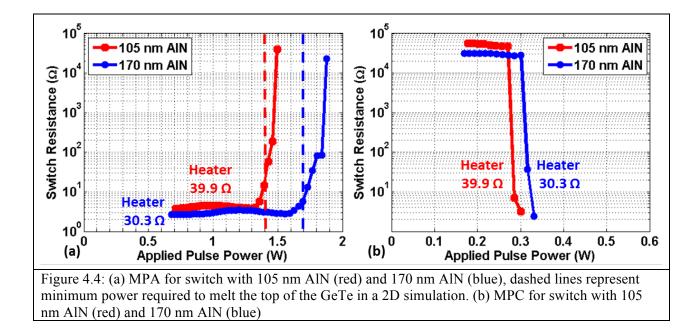

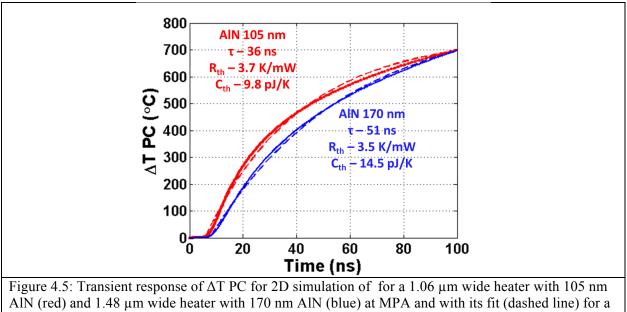

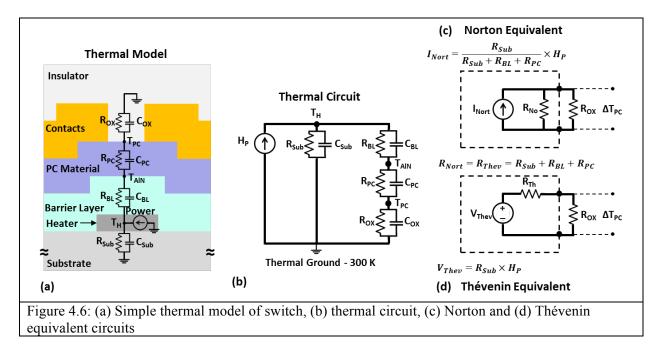

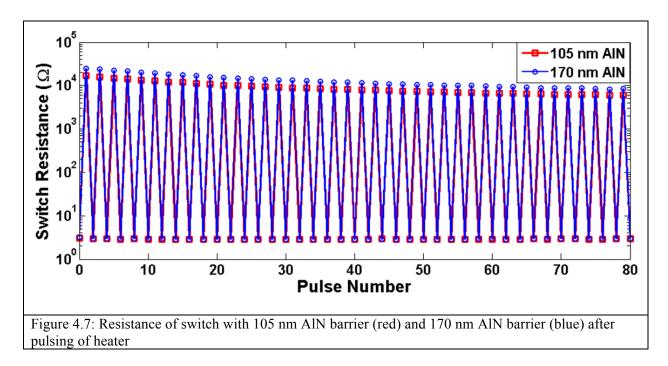

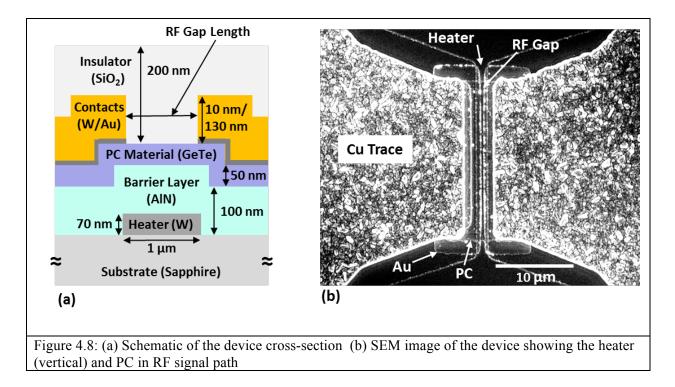

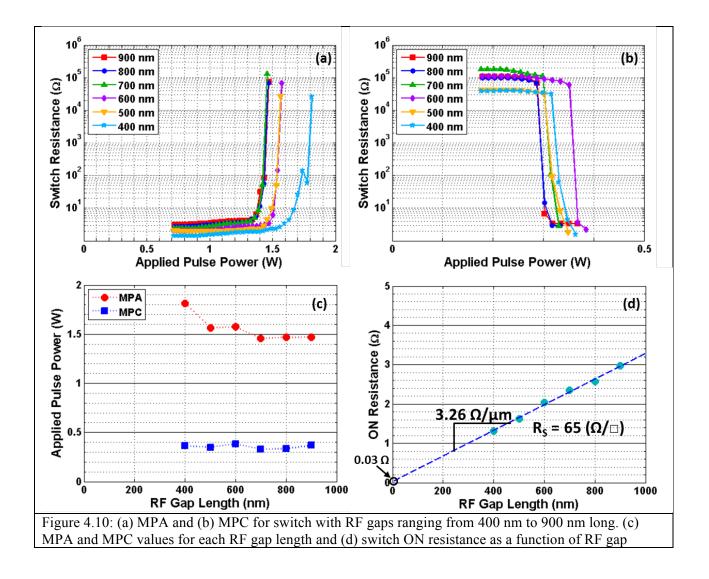

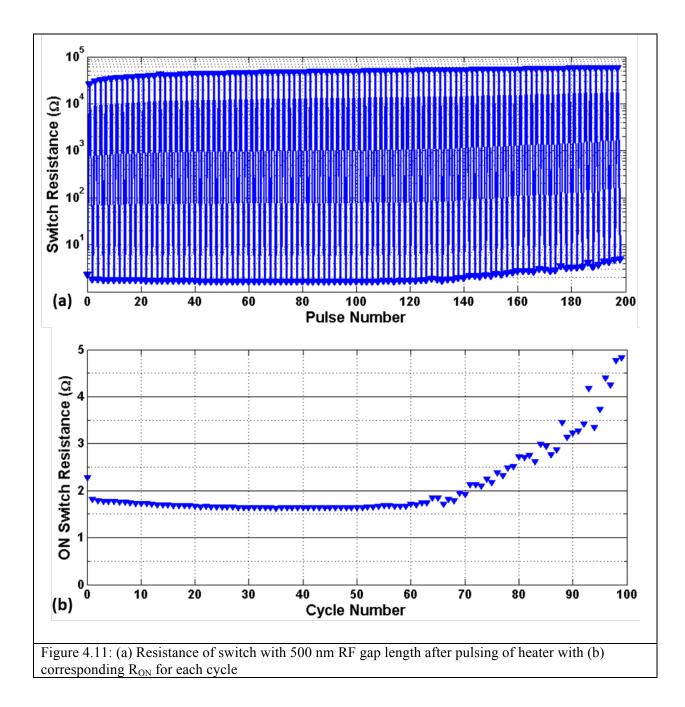

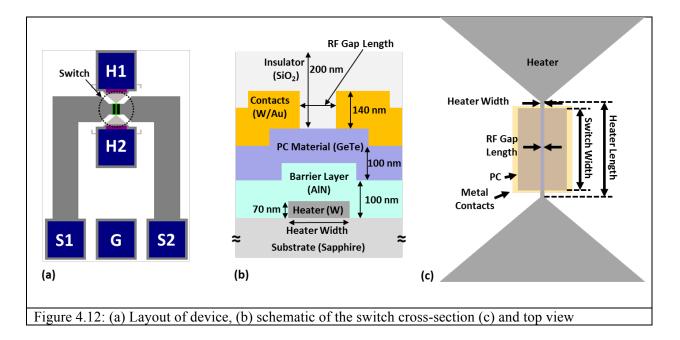

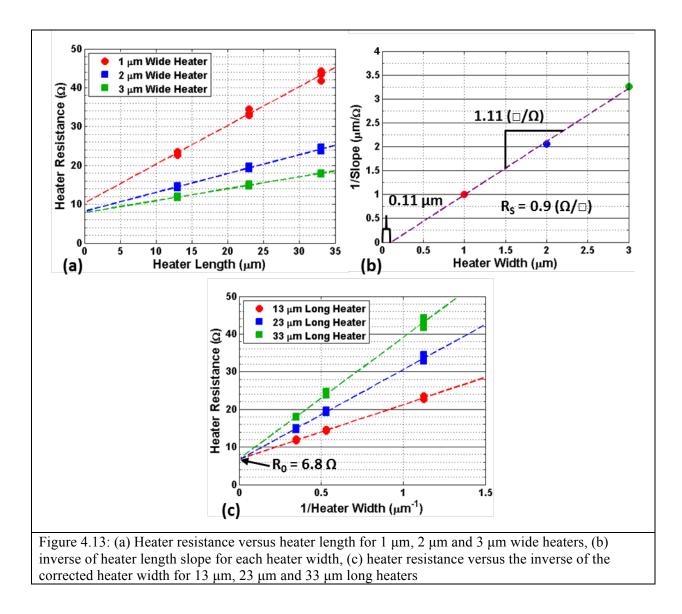

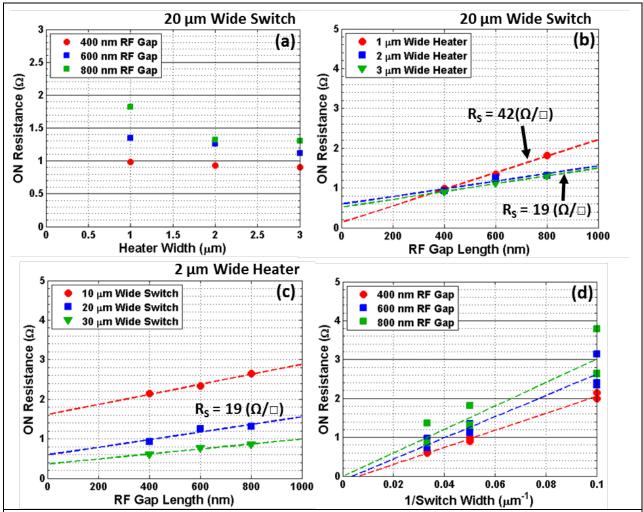

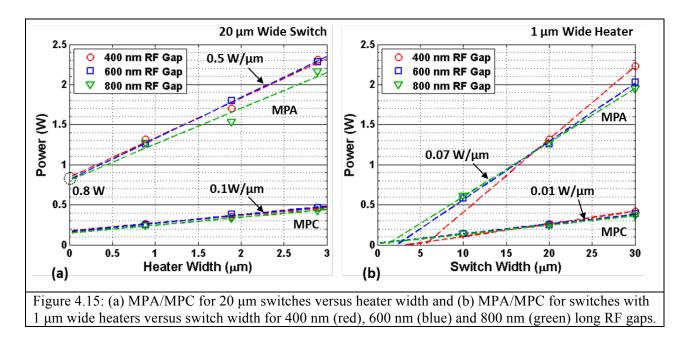

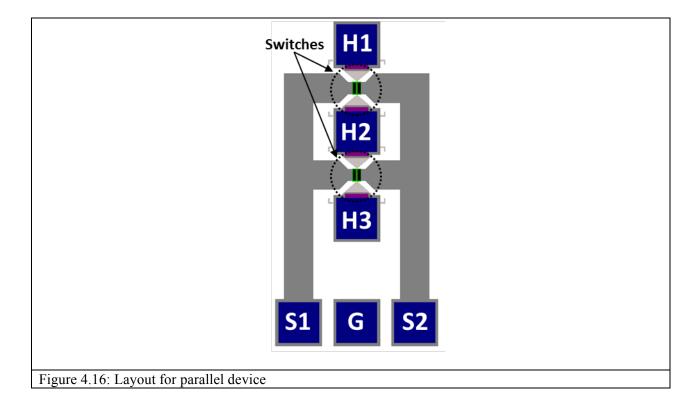

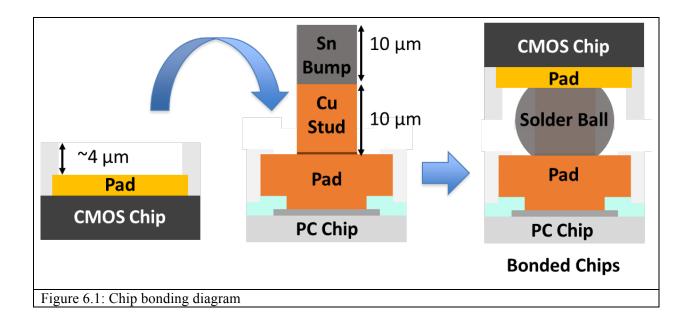

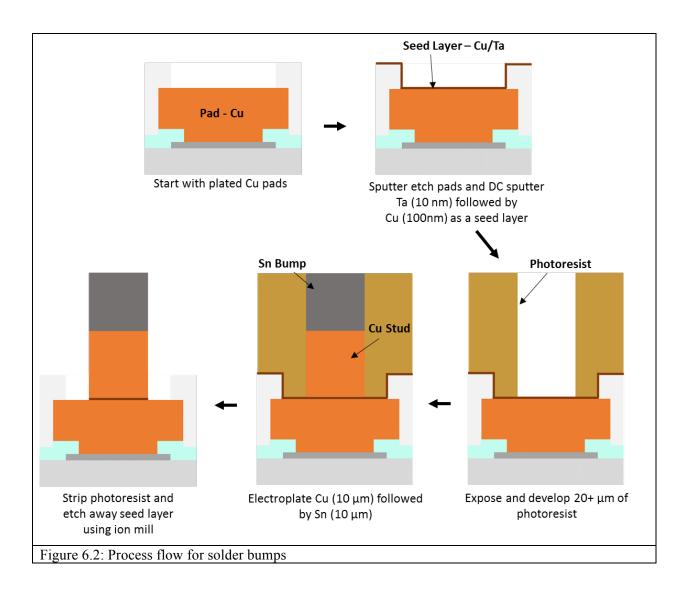

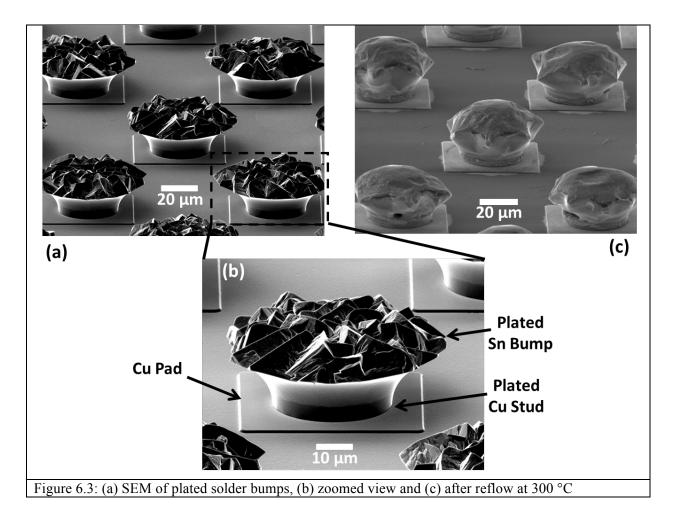

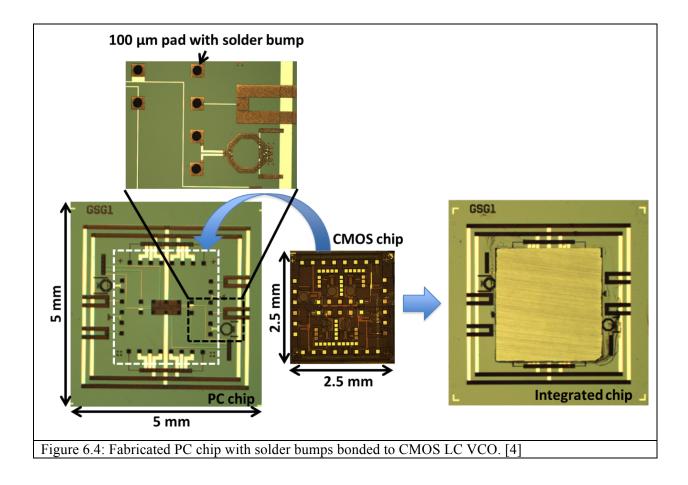

followed by 2  $\mu$ m of plated Cu. The photoresist is stripped and the Ta/Cu seed layer is removed using an Ar<sup>+</sup> ion mill.