### S-type Negative Differential Resistance: Emerging Memory and Oscillators for Next-Generation Computation

A DISSERTATION Submitted in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY Electrical and Computer Engineering

by Abhishek A. Sharma M.S., Electrical & Computer Engineering, Carnegie Mellon University

> CARNEGIE MELLON UNIVERSITY Pittsburgh, Pennsylvania December 2015

### Abstract

Increasing data-centric nature of compute has motivated the need for overcoming the von Neumann memory-access bottleneck. Multi-functional beyond-CMOS have shown a great potential in uniquely complementing and augmenting the compute capability by utilizing emerging paradigms like on-chip memory and brain-inspired computing. In this work, we focus on first understanding the physics of devices that show S-type negative differential resistance behavior (S-NDR) and then engineering them for use in emerging memory (RRAM, selectors) and compute (oscillators for simulated annealing, neural networks, physically obfuscated keys) architectures.

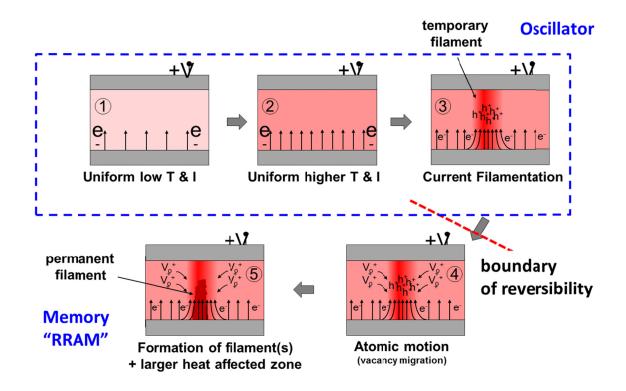

To understand the electro-thermal dynamics of filament formation in metal- semiconductor/oxide -metal (MSM) stacks, we first develop a novel high-speed transient thermometry. This reveals a two-step current localization and nucleation process that is responsible for forming or threshold switching in these MSM stacks. This current localization event manifests as S-NDR in these devices, which we explore to variously understand threshold switching and oscillatory behavior. We also apply the developed nano-scale thermometry to resistive switching memory devices to extract the role of temperature in the switching process. After establishing self-consistency with microstructural changes under a TEM, we estimate the filament size and evolution with bias and current compliance.

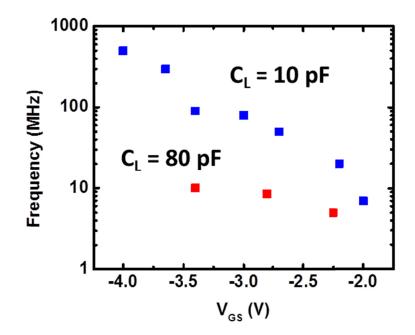

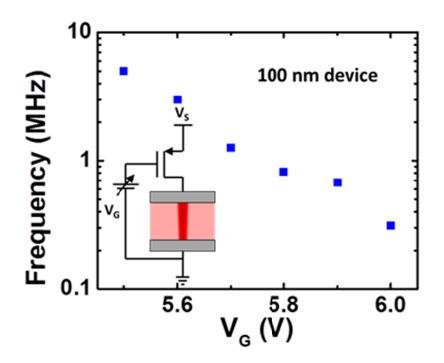

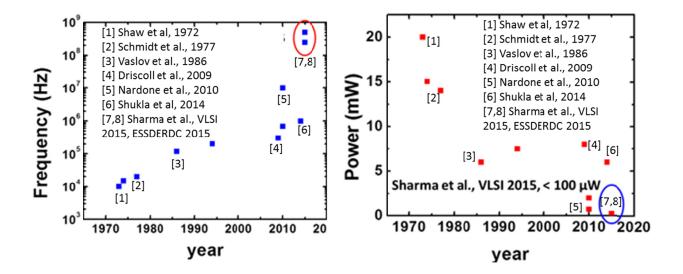

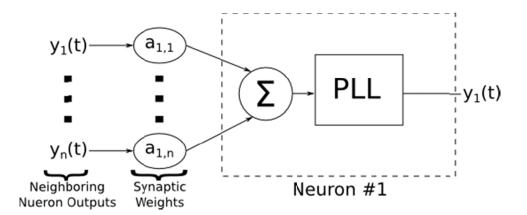

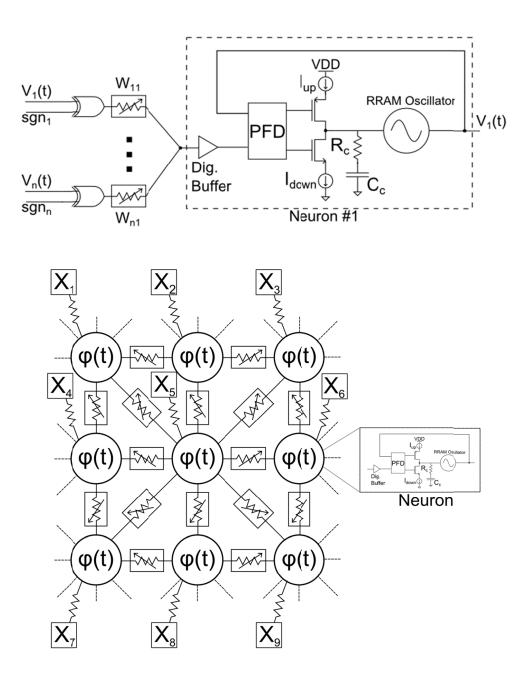

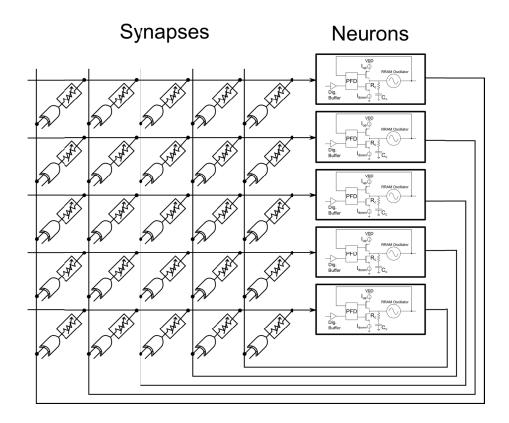

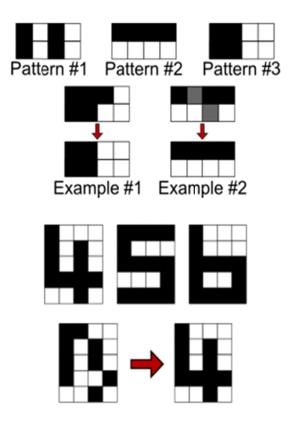

In order to use these S-NDR devices as threshold switches and oscillators, we show for the first time, stack-engineering by changing the material composition, the electrode material and ballast-types to achieve > 500 MHz frequency, < 50  $\mu$ W power, 0.6 V voltage-swing operation as a compact 1T1R oscillator, < 1 V operation, < 1 pA leakage current, ON-OFF ratio of > 10<sup>6</sup>, and a J<sub>ON,max</sub> of > 1 MA/cm<sup>2</sup> for a threshold switch. Finally, using this engineered device, we show demonstrations of oscillator coupling and phase control, injection-locking and noise-reduction. On understanding the role of circuit parasitics on the oscillator behavior, we propose directly-connected simulated annealing for < 100 fJ/compute image feature extraction engine. The application of these oscillators in oscillatory neural networks (ONNs) and entropy sources for generating physically obfuscated keys (POKs) is also explored.

### Acknowledgments

My sincere gratitude and deep respect are towards my advisors Prof. James A. Bain and Prof. Jeffrey A. Weldon for guiding me both technically and otherwise throughout my journey of doctoral studies. With the same breath, I must express my thanks to Prof. Marek Skowronski who also equally contributed to my mentorship. I'd also like to thank my committee members, Malgorzata Jurczak and Charles Kuo for their invaluable inputs throughout my time at Carnegie Mellon. Gratitude to SONIC,GRC,Intel-MSR, Smith Fellowship and others for financial support.

I'd also like to thank different professors and researchers that I worked with and learnt so much from – Andrzej Strojwas, Wojciech Maly, Diana Marculescu, David Greve, Yoosuf Picard, Elijah Karpov, Gilbert Dewey, Charles Augustine, Eriko Nurvitadhi, Lawrence Pileggi. Among peers and seniors, I'd like to thank Jonghan Kwon, Mohammad Noman, Ranga Kamaladasa, Gregory Slovin, Dasheng Li, Darshil Gala, Yunus Kesim, Keiko Nishikawa, Thomas Jackson, Kaustubha Neelathalli. Their contribution to my technical growth has been immense. It is almost impossible for me to think of how I could have accomplished as much as I could without their guidance and help.

If I list all of my close friends that helped to keep me always charged emotionally during my PhD career, it would make for a long list. Hence, I'd like to summarize them in form of the meanings of their names, as can best be translated from different languages to English – Light (x4), Chrysanthemum, Jewel-shard, Lotus (x2), Sun-beam, Foliage, Wisdom, the Ascendant (x2), bringer of thunder, Splendor (x2), Riverine (x3), the Truth that hides, Brilliant Red, Spirit, Rubia, Crescent of the Moon, the Singularity, the Multuplicity, and Rudra. They have all inspired me as much as their names and their nominal meanings are as essential a part of them to me, as they are. I'd also like to thank those who gifted me challenges and grief, for I do not think I could have grown intellectually and emotionally without them. I also thank my students.

Finally, I thank my family – my caring parents and nurturing grandparents, who were my first teachers and continue to sprinkle my life with that which is intellectually captivating and that which is emotionally pleasing. I hope I can unrelentingly rise in life along the routes I set for myself, consuming knowledge, bathing in logic, spirited with emotion and honing with truth.

### **Table of Contents**

| 1. | Introduction                                                                      | 1   |

|----|-----------------------------------------------------------------------------------|-----|

|    | 1.1 Resistive Random Access Memory (RRAM)                                         | 4   |

|    | 1.2 S-NDR Oscillators                                                             | 7   |

|    | 1.3 Thesis Organization                                                           | 9   |

| 2. | Forming in Binary Metal Oxide-based Resistive Switching Memory                    | 12  |

|    | 2.1 Introduction to forming                                                       | 13  |

|    | 2.2 Experimental Techniques                                                       | 17  |

|    | 2.3 DC Forming                                                                    | 20  |

|    | 2.4 Reversibility of forming process                                              | 24  |

|    | 2.5 Voltage-dependent transient measurements                                      | 30  |

|    | 2.6 Temperature, Filament-size and Activation Energy Estimation                   | 32  |

|    | 2.7 Summary of S-NDR in RRAM devices                                              | 47  |

| 3. | Switching Thermometry and Modeling in RRAM                                        | 50  |

|    | 3.1 Introduction to resistive switching                                           | 51  |

|    | 3.2 Thermometry of switched devices                                               | 54  |

|    | 3.3 Microstructural analysis                                                      | 60  |

|    | 3.4 Discussion of pulsed-thermometry                                              | 65  |

|    | 3.5 Endurance cycling                                                             | 67  |

|    | 3.6 Discussion of endurance failures                                              | 68  |

| 4. | S-type Negative Differential Resistance for Compact Oscillators                   | 72  |

|    | 4.1 Introduction to S-NDR oscillators                                             | 73  |

|    | 4.2 S-type Negative Differential Resistance and Oscillations in TaO <sub>x</sub>  | 75  |

|    | 4.3 Effect of resistor and transistor ballast                                     | 79  |

|    | 4.4 Discussion on scalability, variability, failure modes and performance metrics | 86  |

| 5. | Engineering S-NDR Oscillators                                                     | 90  |

|    | 5.1 Introduction to S-NDR performance metrics and challenges                      | 91  |

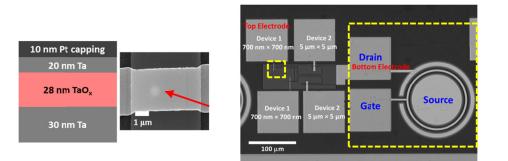

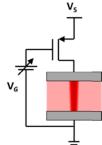

|    | 5.2 Device structure and transistor integration                                   | 94  |

|    | 5.3 Engineering oscillators for low-power and high-performance                    | 96  |

|    | 5.4 Discussion of physics of scaling                                              | 100 |

|    | 5.5 Oscillatory Neural Networks (ONNs)                                            | 103 |

| 6. | S-NDR Oscillators: Network Applications                                           | 113 |

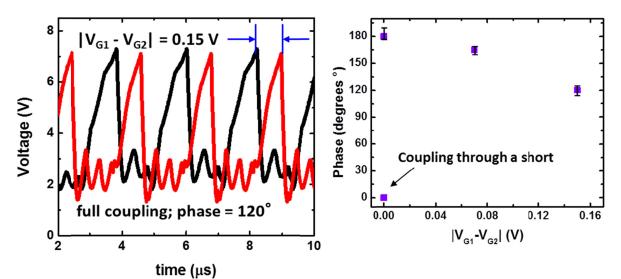

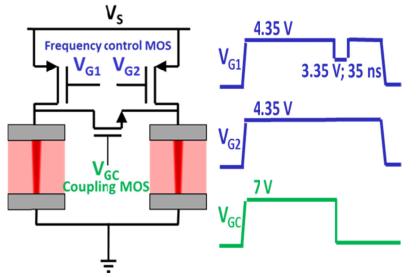

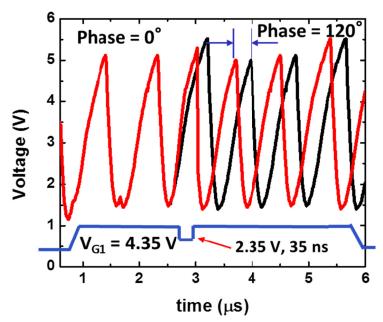

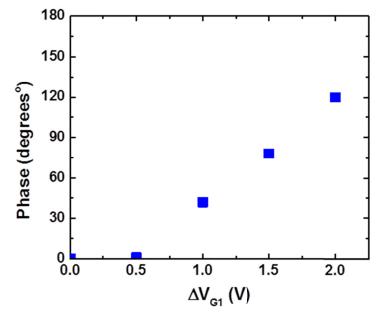

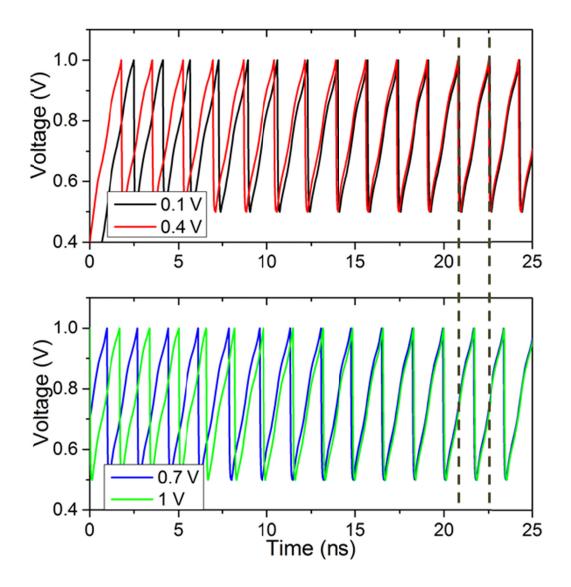

|    | 6.1 Phase coupling and control of S-NDR oscillators                               | 116 |

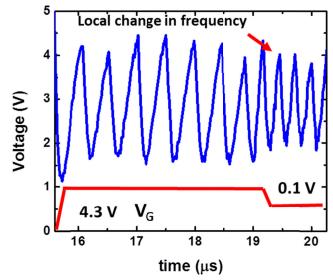

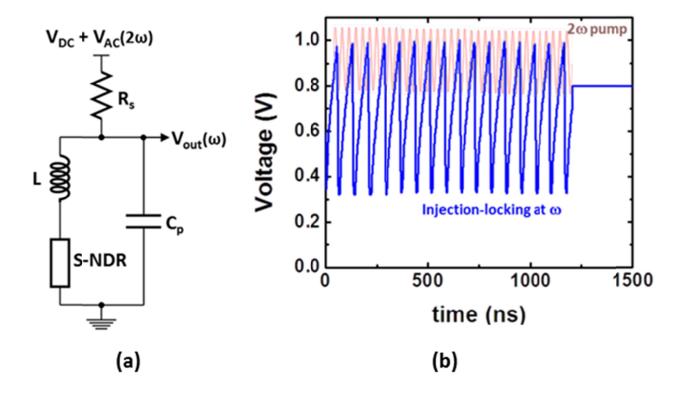

|    | 6.2 Sub-harmonic injection locking                                                | 125 |

|    | 6.3 Edge detection using directly coupled networks                                | 128 |

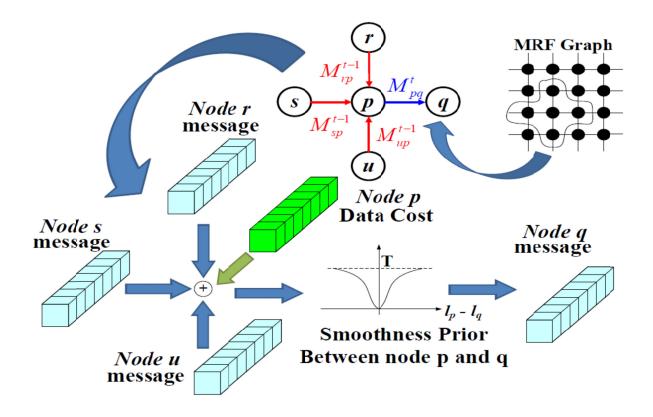

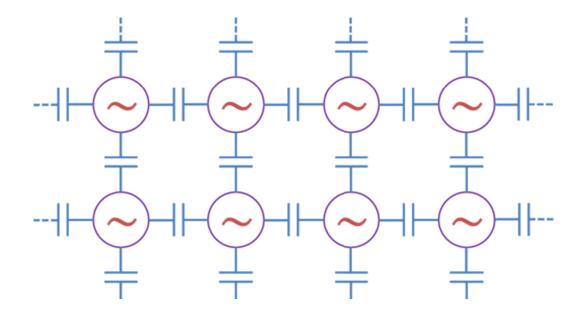

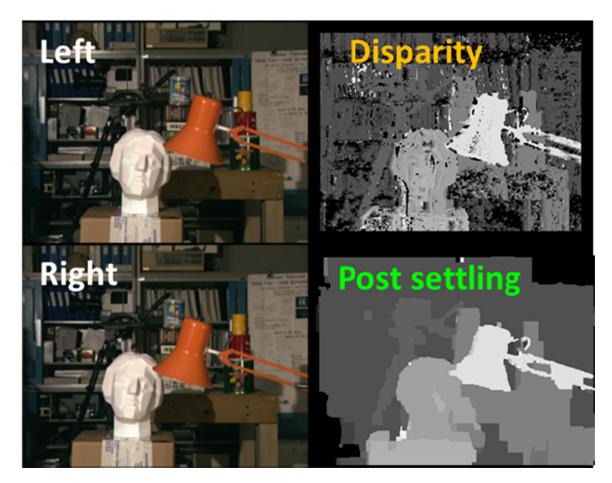

|    | 6.4 Stereo vision using coupled oscillator networks                               | 134 |

|    |                                                                                   |     |

| 7. | Conclusion                                                                                              | 140 |

|----|---------------------------------------------------------------------------------------------------------|-----|

| 8. | References                                                                                              | 143 |

| Ар | opendix A: Review of thermometry and modeling parameters, and comparison<br>with existing methodologies | 155 |

| Ap | opendix B: Low-temperature forming process                                                              | 168 |

| Ap | opendix C: VerilogA model of S-NDR devices                                                              | 180 |

# Chapter 1

## Introduction

Increasing data-centric nature of computation has motivated the need for overcoming the memory-access bottleneck, also known as the von Neumann bottleneck. In massively parallel computational tasks, such as pattern recognition, conventional computing architectures have insufficient power efficiency for energy constrained environments. Thus, multi-functional beyond-CMOS have shown a great potential in uniquely complementing and augmenting the compute capability by utilizing emerging paradigms like on-chip memory and brain-inspired computing. By design, modern computer architecture assumes spatio-temporal locality of data and hence tries to maximize the data loaded in cache located on chip. If the desired data is not found in cache, it has to go off-chip to access the main memory (DRAM) and eventually storage (HDD/SSD). The latencies associated with data access range from ns for SRAMs and DRAM; and ms scale for HDDs. Most of this delay comes from transit delay associated with going offchip or from mechanical access. This problem is exacerbated in data-intensive applications like image processing. Two possible methods of resolving this problem are: (1) Integrating a storage class memory at the backend of the line (BEOL) [1] or (2) Parallelizing compute using braininspired graphical methods [2]. As flash scaling is reaching its limits [3]-[5], newer memories like resistive random access memory (RRAM) and magnetic random access memory (MRAM) are being looked at, as a storage-class flash replacement and DRAM replacement [1] respectively. Similarly, some of the emerging devices like Carbon nanotubes (CNTs), RRAM and S-type negative differential resistance (S-NDR) oscillators can be utilized as a BEOL graphical processing engine for increased compute parallelism. These unique devices exhibit physical and electrical properties that make them uniquely suited to improve compute without the need for the expensive wafer stacking using interposers and through-Si-vias (TSVs). Moreover, because the operation of these devices involves a fundamentally different mechanism

than, for instance, transistors, they can enable novel methods of compute for which CMOS is comparatively inefficient.

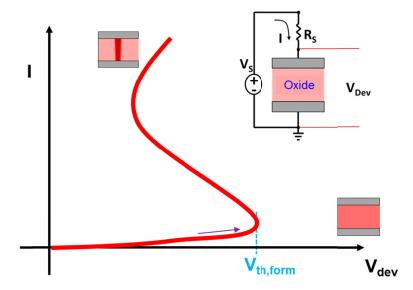

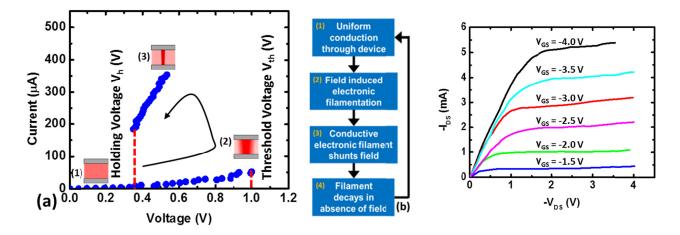

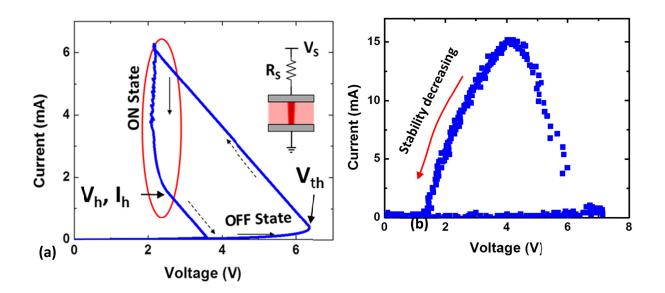

Transistors, which form the basic building block of modern electronics, show tremendous versatility as multi-functional devices. In quest for another multi-functional device that can complement modern computation, we will focus this work on devices that exhibit S-type negative differential resistance or S-NDR. This work will attempt to interrogate these S-NDR devices to explore their potential as a transistor-like building block. Figure 1.1 shows a typical I-V schematic of a device with S-NDR characteristics.

**Fig. 1.1**: Figure showing schematic I-V characteristics of an S-NDR device. The inset shows a schematic circuit diagram and stack that is used to generate the I-V.

The device shown in Fig. 1.1 is a leaky metal-insulator-metal stack. As fabricated, these devices have a very high resistance (also referred to as the pre-formed or OFF state), as shown in the I-V curve at low biases and currents. In this regime, the resistance (V/R) and the differential

resistance (dV/dI) are both positive. As the source bias is increased for this circuit beyond the labeled threshold or forming voltage, V<sub>th,form</sub>, the device enters a negative differential resistance regime where the voltage across the device decreases as the current increases. If the bias is increased further, the device again reverts to a positive differential resistance, with a much lower resistance than the OFF state. This regime is known as the ON-state. Previous works [6] have proposed that the OFF-state corresponds to uniform conduction through the device whereas the ON-state corresponds to the device conducting locally. Associated with this localization event, the electrical properties of the device can thus be tuned temporarily or permanently. As the S-NDR element is a simple MIM/MSM stack, they can be integrated in large and dense cross-point arrays [11] with of minimum-pitch (4F2 footprint) that the lithography can provide. Moreover, as the conduction mechanism of these devices is filamentary in nature in the ON-state, they can be scaled to very small footprints of ~ 10 nm [9].

In this work, we focus on first understanding the physics of devices that show S-type negative differential resistance behavior (S-NDR) and then engineering them for use in emerging memory (RRAM, selectors) and compute (oscillators for simulated annealing, neural networks, physically obfuscated keys) architectures. The central idea is to integrate the working of S-NDR devices as memory units with their oscillatory response under the same framework.

#### 1.1. Resistive Random Access Memory (RRAM)

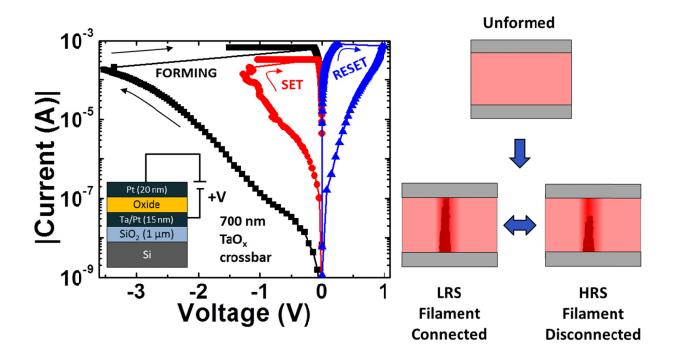

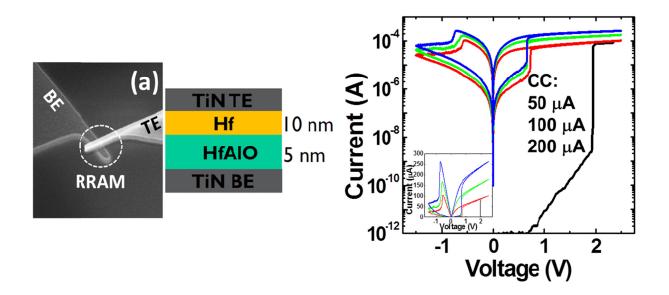

RRAM devices generally have a very simple metal/oxide/metal heterostructure as shown in Figure 1.2, akin to the S-NDR devices explained in the previous section. The oxide thickness is usually in the range of 2-50 nm. Over the last few years, many different oxides have been found

to display resistance switching characteristics.  $TiO_x$ ,  $HfO_x$ ,  $TaO_x$ ,  $NiO_x$ ,  $AlO_x$ ,  $SiO_x$  [7], etc. are just a few examples of this. Pt, Ti, TiN, and Al are some of the typical metals used for the electrodes. The resistance switching in these devices is typically represented by the current-voltage (*I-V*) curve shown in Fig. 1.2.

**Fig. 1.2:** A typical RRAM device (in this example  $TaO_x$ ) undergoing forming (black), RESET (blue) and SET (red), alongside common visualization of the physical origin of resistance change in form of filament connection and disconnection.

These devices do not start off as being resistive switching memories; they have to go through a one-time programming process known as forming or electroforming. The forming process involves the application of a high voltage pulse that causes the oxide to breakdown and form a conductive filament that shunts the two metal electrodes, causing the resistance to decrease [8]. The LRS corresponds to the shunted conductive filament. This filament can be disconnected by

applying a voltage of the opposite polarity (referred to as RESET). Once the conductive filament is disconnected, the device resistance increases, and the device is said to be in the HRS. Applying a voltage of the same polarity as forming, causes the device to revert back to the LRS (referred to as SET). The device can now be cycled between the two states. The nature of the conductive filament is still a matter of debate. Typically, the conductive filament is assumed to be made up of a reduced oxide (sub-oxide) phase that is conductive in nature, often referred to as an agglomeration of oxygen vacancies (absence of oxygen atoms).

As memory (RRAM), these resistive switching devices have shown to offer great potential in terms of compactness & scalability [9], endurance [10], integration [11] and power efficiency [9]-[10]. Additionally, despite being an area of research since past 4-5 decades, it still continues to generate exciting questions regarding the fundamental nature of electronic conduction and ionic motion. While a huge corpus of research exists in dielectric breakdown phenomenon and resistive switching, one of the most significant challenges associated with commercialization of RRAM is the lack of depth in understanding the resistive switching physics, thus resulting in several often circumstantially degenerate models with limited predictive ability [12]-[15]. In this work, we will develop novel electro-thermal characterization techniques that can guide existing models. In this work, we will discuss how the forming process, which is central to the device operation as a memory (post-forming), is a natural extension of the S-NDR behavior that these devices exhibit pre-forming. As per the explanation of S-NDR behavior from the previous section, the devices that undergo forming process are biased in the ON-state of the S-NDR I-V curve. If the ON-state is maintained even after the bias has been removed, it implies that the devices has permanently changed, or formed or 'memory switched'. If the ON-state is volatile, the device in ON-state is considered to be 'threshold switched'. This will help us in addressing

the challenges associated with the physical understanding of the forming and subsequently switching process. Specifically, this work will attempt to examine the following questions: (1) What are the steps preceding the forming process? (2) What initiates vacancy migration? (3) What are the peak temperatures reached during the forming and switching process? (4) What is the role of temperature in the conductive filament formation and vacancy migration during forming and switching? (5) What controls the peak filament size during forming and switching? (6) What is the role of temperature in endurance failure of RRAM devices?

#### **1.2. S-NDR Oscillators**

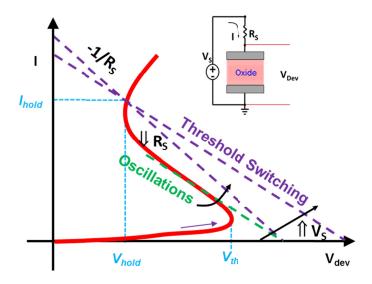

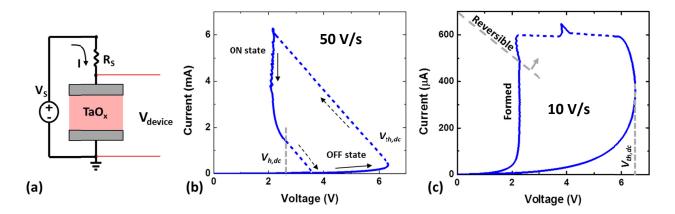

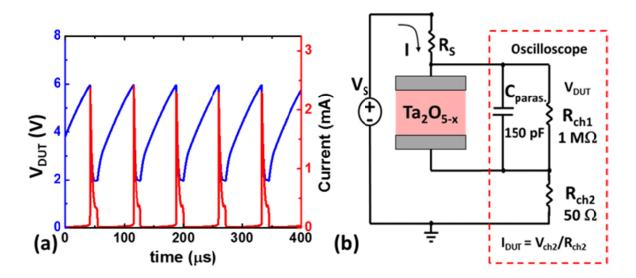

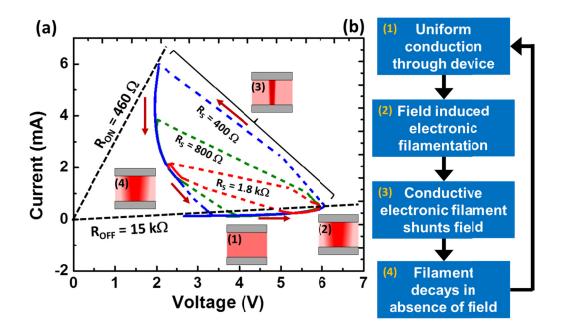

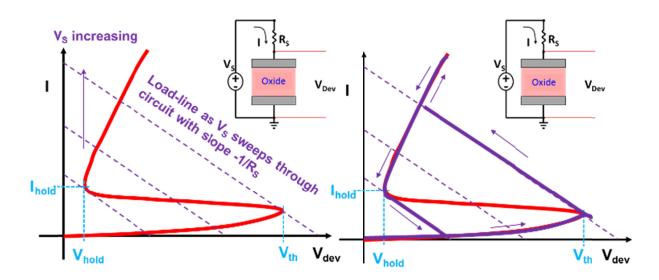

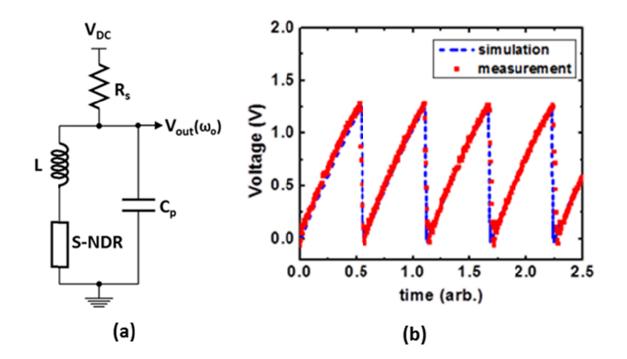

Using the preliminary understanding of resistive switching obtained in the initial course of this study; we will also explore the possibility of using a similar device stack as an oscillator for brain-inspired oscillatory neural networks. These oscillatory elements utilize threshold switching phenomenon that exists in several sub-stoichiometric transition metal oxides, a phenomenon often associated with electronic localization effects that eventually lead to oxide breakdown [16]. Specifically, when the devices are biased in the negative differential resistance regime, they exhibit sustained relaxation oscillations, as shown in Figure 1.3 (intersection of the green dotted line with the I-V shows the bias-point corresponding to oscillatory behavior). Similarly, if the devices are biased to a higher current value in the ON-state, the device will undergo threshold switching i.e. settle to an ON-state. Depending on the material parameters (whether or not it undergoes forming or not), the device will remain in the ON-state till the bias is maintained, a phenomena referred to as threshold switching. Once the bias is removed, the device will revert back to the unformed OFF-state (violet dotted line represents the bias point required for threshold switching).

Fig. 1.3: I-V schematic of an S-NDR device oscillatory and threshold switching bias-points.

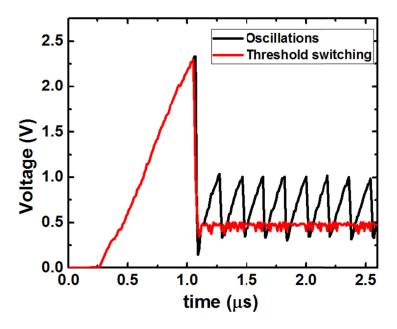

Figure 1.4 shows the coexistence of oscillatory (black) and threshold switching (red) response in these devices.

Fig. 1.4: Coexistence of oscillatory and threshold switching response in a typical S-NDR device.

As threshold switches, these device find applications as two-terminal threshold switch selectors for cross-point memories [17]. As oscillators, these devices thus serve as interesting building

blocks for large arrays, offering the possibility of coupling, compactness, and power efficiency in oscillator networks. However, the major challenges faced by this class of devices are: (1) Lack of physical understanding of the threshold-switching/oscillatory response, (2) High voltage and power needed to operate these devices, and (3) Poor understanding of co-design needed between device design and circuit topology connected to the device. This work will use TaO<sub>x</sub> as a demonstration vehicle to show co-existence of memory switching, threshold switching and oscillations. Current attempts at engineering these devices for low-power and high-performance have met with limited success. In this thesis, we will generate an understanding of these oscillatory devices so as to engineer them for low-power and high-performance. Specifically, this thesis will explore the following questions: (1) What determines the transience of the ON-state? (2) How are threshold switches/oscillators different from memory switches? (3) What sets the performance metrics of the oscillator and how can it be modified?

#### 1.3. Organization of thesis document

This document consists of a total of six chapters and a conclusion. The first chapter introduces the concept of S-NDR and its relationship with RRAM devices and oscillators. Detailed literature survey is intentionally left out to maintain high-level simplicity; literature will be surveyed at the beginning of each chapter for details. As the final goal is to attempt to shed light on the multi-functionality of the S-NDR element, we will first attempt at understanding the physics behind the device operation. This involves the understanding of the threshold switching/forming process. The forming process controls the filament diameter and its properties; however, it is a failure mechanism for threshold switches and oscillators that are created out of S-NDR devices. Chapter 2 will discuss the reversibility of the filament formation during the formation process, thus clearly separating the difference in forming and threshold switching/oscillations. For this purpose, we develop a novel high-speed thermometry to understand the process of localization and the associated temperature excursions. In Chapter 3, we use the same thermometry to determine the filament properties (size, temperature, electrical properties etc.) of an RRAM device in the LRS. Thermometry in switched devices enables us to understand the role of temperature in switching, the microstructural changes that accompany these temperature excursions and failure mechanisms.

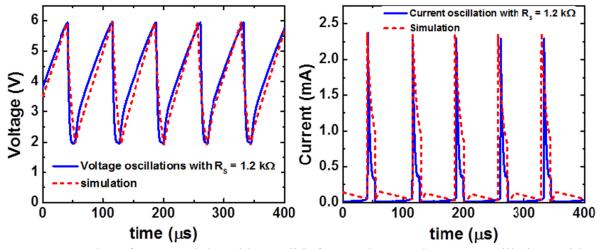

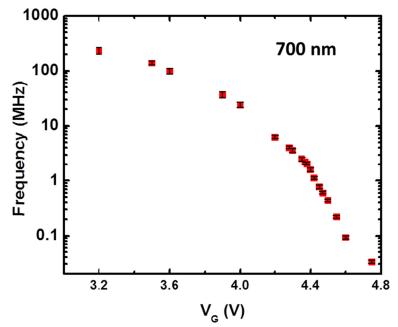

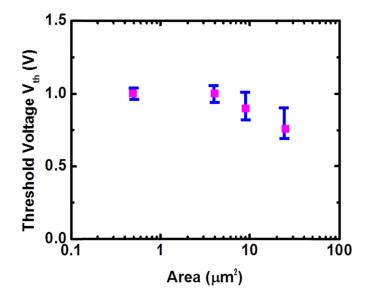

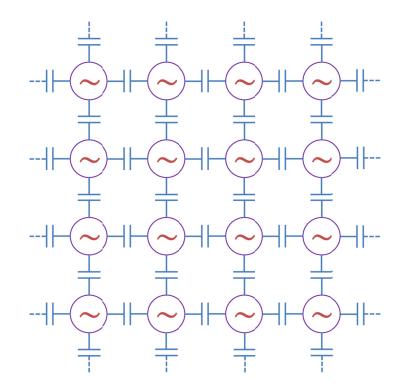

Chapter 4 revisits the S-NDR devices and discusses the origins of oscillations in TaO<sub>x</sub>-based devices, clearly highlighting origin of frequency control, the role of parasitics and ballasts on the oscillation response. The devices explained in Chapter 4 cannot be used as is, for computation; they have to be engineered for low-power and high performance. Chapter 5 delves into the stackengineering of  $TaO_x$  –based oscillators to yield the best-in-class oscillator (in terms of power and performance) and explores its use in oscillatory neural networks (ONNs). While compact oscillators provide unique advantage for dense array implementations, the CMOS circuitry around ONNs makes the implementation both power and area inefficient. We also discuss scalability in area and power, and variability in these oscillators. Thus Chapter 6 discusses how these oscillators can be directly coupled using unique physics that maintains the temporary ONstate in presence of coupling elements like capacitors. With this, we demonstrate for the first time, coupled oscillator pair with full phase coupling and control using transistors. To overcome some of the challenges discussed in Chapters 2, 4 and 5, we demonstrate injection-locking in these oscillators. This enables us to program the initial phase of these oscillators using a global clock and reduce the drift in frequency due to aging. In order to simulate dense parallel systems with these oscillators, we first develop a SPICE model of these relaxation oscillators using van der Pol's formalism, which is a second order non-linear differential equation. Using this equation, we then construct a fully connected oscillator network and program it for robust image feature extraction engine. Using similar concepts, we finally demonstrate a full simulation of a stereo vision engine that utilizes the unique parallelism that is offered by the oscillator arrays to efficiently implement data and smoothness costs. A full scale foundry PDK and data driven SPICE simulation is described to understand the unique advantages that these networks offer for energy minimization-type problems.

## Chapter 2

## Forming in Binary Metal Oxide-based Resistive

**Switching Memory**

#### 2.1. Introduction to forming

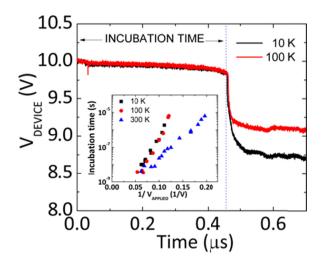

Binary oxide-based resistive switching devices have shown a great potential as the nextgeneration non-volatile Resistive Random Access Memory (RRAM) elements [18]. These memory cells are based on changes in resistance thought to be due to the change in the stoichiometry of the oxide which typically becomes more conductive when deficient in oxygen [19]. It is now well established that the change of resistivity occurs only locally within a small diameter filament [7]. The switching between high and low resistance states (OFF and ON states, respectively) is thought as due to changes of the vertical extent of the filament [7],[20] or a formation of a lateral constriction within the filament [21]. Before a device can be switched, it has to undergo an initialization process referred to as the electroforming or simply the forming step. During this process, a voltage is applied to the device resulting in the creation of an metallic filament in the initially uniformly conducting device. Even though the forming establishes the active area of the device and determines many of its characteristics, very few reports have addressed the complex details of this process [22]-[25].

Recent experimental results on oxide-based devices indicate that the formation of a permanent conducting filament is not instantaneous. Instead, after application of a bias pulse, the device retains its high resistance for the time referred as the incubation time after which the resistance rapidly decreases. This process is associated with current localization, as the initially uniform current flow spontaneously localizes to a narrow filament. The incubation time is strongly dependent on applied voltage and temperature [26],[27]. It was also observed that the initial decrease of resistance is volatile i.e. if the voltage pulse is terminated soon after the drop of resistance (typically less than 1  $\mu$ s), the device will return to its original highly resistive

unformed state. Only after the voltage is maintained for sufficiently long time, does the resistance change become permanent [24]. Similar phenomenon is well documented in chalcogenide-based phase change memory (PCM) where volatile resistance drop is referred to as threshold switching (with retention times of less than 1  $\mu$ s) and is distinctly different from memory switching (with retention time of years) [28],[29].

The dynamics of the switching process is best described by a classical nucleation switching theory [31] applied in the past to interpret the results on chalcogenide [30] and oxide devices [31]-[34]. We note that the model is universal and has been applied to describe phase transitions of different physical nature, both involving the amorphous-crystalline transition in chalcogenides and those involving electronic changes, for example, Mott transitions in strongly correlated oxides [33]-[34]. However, it must be noted that the nucleation model does not specify the exact nature of the conductive phase. Thus, this phase could be either an electronic phase or a structural distortion. The model is briefly described here for the reader's convenience. It interprets the sudden drop in resistance as due to the nucleation of a conductive second phase inclusion in the functional layer under bias. This inclusion changes the free energy of the system,  $\Delta G$ , by:

$$\Delta G = A\sigma + \mu \Omega + W_{\rm F} \tag{2.1}$$

where the first term describes the energy of the interface between the two phases with A being the nucleus surface area and  $\sigma$  being the interface energy per unit area. The second term is a volumetric change, with  $\mu$  being the free energy difference between the insulating and conducting phases per unit volume, and  $\Omega$  is the nucleus volume. This term, if  $\mu$  is negative, can lead to spontaneous nucleation of the conductive phase at elevated temperatures in absence of the

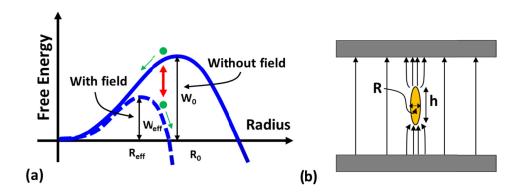

field. In the dielectric materials here, the nucleation model could describe the transition between the insulating disordered oxygen vacancies phase, and the small inclusion of conductive phase consisting of ordered vacancies. This inclusion can nucleate at any non-uniformity in the material, and will grow into a filament when the growth is thermodynamically favorable. The reduction of an energy barrier for a formation of a vacancy pair when two vacancies are close has been theoretically predicted for oxide materials, supporting that cluster and ordered vacancies filament formation is energetically favorable. Clustering was experimentally observed in TiO<sub>2</sub> single crystals with applied bias and ordered vacancy phases known as Magnéli phases had been observed in TiO<sub>2</sub>-based RRAM devices [19]. Although the oxygen-vacancy model appears to be the leading interpretation of resistance switching in oxides, we do not want to exclude the possibility that the conducting phase is of different, as of yet unidentified, nature. One such possible phase transition would be an insulator-metal Mott transition in Ti and Ta suboxides. The nucleation of the inclusion of the critical size  $R_0$  is delayed by the incubation time due to nucleation barrier ( $W_0$  in Fig. 2.1) associated. The last term in Eq. (2.1) is the electrostatic energy associated with the conductive 'inclusion' (as shown in Figure 2.1 (b)) in the charged parallel plate capacitor. This term grows more negative with the applied electric field and causes the nucleation barrier to decrease ( $W_{eff}$  in Fig. 2.1). The barrier reduction lowers the incubation time. In parallel with decreasing the barrier, the electric field causes the size of the nucleus corresponding to the maximum of energy to shrink  $(R_{eff} < R_0)$ . This has important consequences. For example, if the statistical fluctuation in the functional layer under bias produced a nucleus with size  $R < R_{eff}$ , such nucleus is expected to dissolve. Only the larger nuclei  $(R > R_{eff})$  should be stable and grow in the presence of field. It is evident that the inclusion which, in the presence of field, is stable and starts to grow  $(R_{eff} < R < R_0)$ , would become subcritical and dissolve if the bias is removed. This, in the nucleation switching model, is the origin of the initial volatility of the ON state.

**Fig. 2.1:** (a) Free-energy curve showing the lowering of barrier in presence of field (from  $W_0$  to  $W_{eff}$ ). (b) A prolate ellipsoid inclusion assumed in the field-induced nucleation theory.

When a filament grows sufficiently large, it becomes non-volatile, i.e. stable after the external field is removed. The temporal dynamics of nucleation switching can be described as follows:

$$\tau = \tau_0 \exp\left(\frac{W_{eff}}{kT}\right) \tag{2.2}$$

Where,  $W_{eff}$  is a nucleation barrier, given by the maximum of the free energy  $\Delta G$  in Eq. (2.1) along the nucleation trajectory. At high voltages, this expression can be approximated by the simple analytic expression:

$$\tau = \tau_0 \exp\left(\frac{W_0}{kT} \frac{V_0}{V}\right) \quad (V > V_0)$$

(2.3)

Here,  $V_0$  is the voltage acceleration factor (a constant expressed in Volts and approximately independent of device voltage and temperature). The term  $W_0$  represents the barrier height at zero applied voltage. Its value is determined by the volumetric ( $\mu$ ) and interfacial ( $\sigma$ ) energy densities. *T* is the device temperature and  $\tau_o$  is the attempt frequency.

In this chapter, we have measured the incubation time ( $\tau$ ) as a function of applied bias and stage temperature for TaO<sub>x</sub> and TiO<sub>x</sub> crossbar devices, extracted the activation energy for the incubation time as a function of applied voltage, and applied a nucleation model which was extended to include a self-heating effect in dielectric film to explain the data. We find that the model very well describes the complex functional dependence of  $\tau(V, T)$ . The extracted parameters of the nucleation switching model are compared with data available from other experiments. To understand the nature of the forming process better, we also conduct DC testing of RRAM devices in the presence of resistive ballast to understand the process of filamentation that precedes the forming process. The complex functional dependence of temperature and voltage are then utilized to estimate the temperature as the device undergoes filament formation process.

#### **2.2. Experimental Techniques**

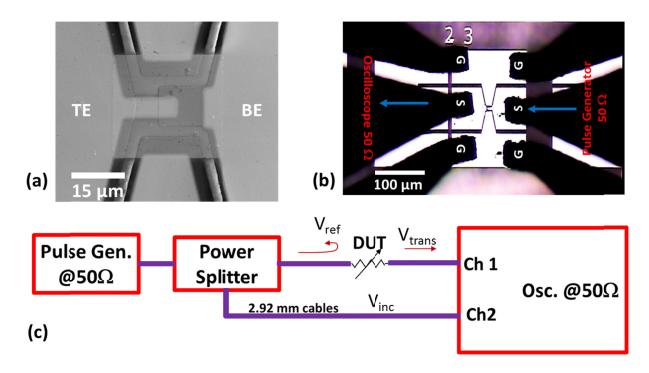

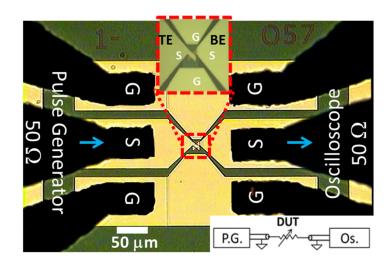

The devices used in this study were  $TaO_x$ - and  $TiO_x$ -based metal-insulator-metal (MIM) crossbars designed specifically for high-speed pulse forming experiments. The vertical MIM stacks consisted of 15 nm Pt / 60 nm  $TaO_x$  / 5 nm Ta / 10 nm Pt and 15 nm Pt / 15 nm  $TiO_x$  /5 nm Ti / 10 nm Pt, respectively. The top view of the device at two different magnifications is shown in Fig. 2.2 (a) and (b). The devices have been designed to be a matched 50  $\Omega$  air-coplanar waveguide in a Ground-Signal-Ground configuration. Moreover, 50  $\Omega$  characteristic impedance as seen from the source (pulse generator), the oscilloscope port, and the 2.92 mm cables (40 GHz bandwidth) ensured that the pulse consistency was maintained and there were no parasitic reflections. The switching dynamics was measured using a time domain transmissometry (TDT)

(in order to get better measurement accuracy than time domain reflectometry) method which allows for monitoring high-speed transients without interference of parasitic reflections [35].

Fig. 2.2: (a) SEM image of the device. (b) Top view of the air-coplanar waveguide (ACPW) device with GSG RF probes with a pitch of 100  $\mu$ m (23 in the image is the device ID). (c) Time Domain Transmissometry 50  $\Omega$  RF setup schematic.

Figure 2.2 (c) shows a schematic of the TDT setup. In TDT experiment, a pulse is launched from a pulse generator into one of the three ports of a resistive power splitter. Part of the signal is then propagated to one of the oscilloscope channels where it serves as the reference or incident signal. The third port of the power splitter is connected to the device through microwave probes and finally terminates at an oscilloscope port with 50  $\Omega$  impedance. Part of signal that is incident on the device is reflected back while the remaining part is transmitted to one of the channels of the oscilloscope. Thus, the oscilloscope can record both the incident and the transmitted waves. Knowing these, one can calculate the transmission coefficient ( $\tau$ ) and knowing the characteristic impedance of the line ( $Z_0$ ), one can extract the voltage across the device, the current flowing through the device and the resistance transient at the device. More details about the setup is explained in Appendix A.

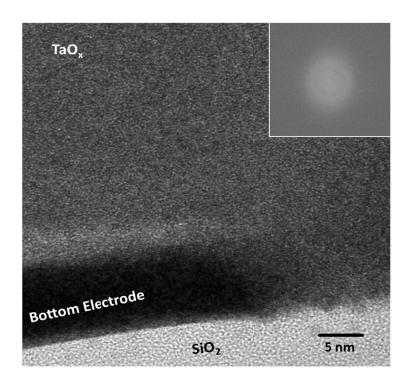

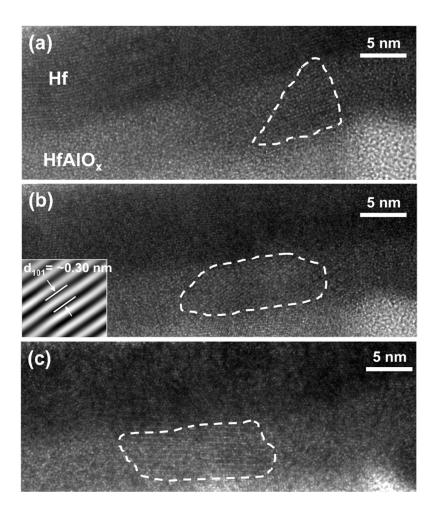

**Figure 2.3**: Bright-field TEM image of the sample with FFT pattern as an inset showing amorphous microstructure.

The functional films were deposited at room temperature and because of that should be amorphous. This was verified by a high-resolution TEM. Fig. 2.3 shows a HR TEM image of the structure while the inset shows a Fast Fourier Transform pattern of the functional layer image. The lack of any discernible directional intensity changes indicates the amorphous nature of the film.

#### 2.3. DC Forming

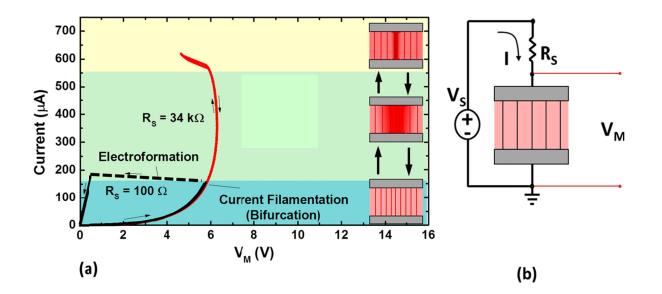

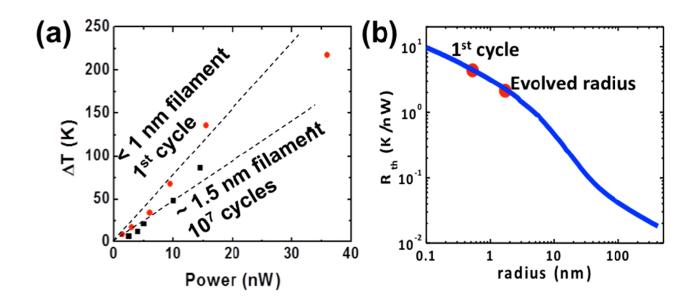

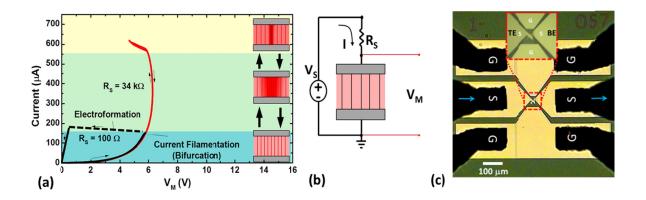

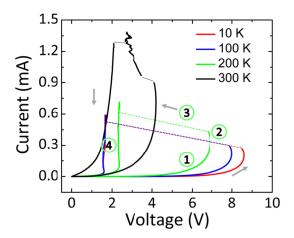

**Fig. 2.4:** Observation of negative differential resistance (NDR) in  $Ta_2O_{5-x}$ . (a) Electroformation with a 'snap' observed in samples with 100  $\Omega$  series resistance (black trace). This is prevented by using a large source resistance (red trace). Stable and reversible current filamentation causes the device *I-V* to show negative differential resistance (NDR), postbifurcation. The three color-zones indicate uniform conduction (blue), thermal filamentation (green) and filament collapse (yellow). Inset on the right shows a schematic of the change in conducting area as the device is driven to filamentation. (b) Circuit schematic shows the experimental setup with V<sub>M</sub> representing the device voltage.

Figure 2.4 shows four quasi-DC *I-V* characteristics obtained from a single crossbar-type Pt/Ta<sub>2</sub>O<sub>5</sub>/Pt device. The two curves were obtained using different values of series resistor,  $R_s$  (the circuit schematic is shown in Fig. 2.4(b)). The measurements were made by sweeping the source voltage while measuring the voltage across the device ( $V_m$  in the figure). Because increasing the series resistance in the circuit decreases the slope of the load-line (which is -1/R<sub>s</sub>), a higher voltage from the source is needed to reach the same *I-V* point of the device. The black line marks the *I-V* obtained with  $R_s = 100 \Omega$ . Starting at low voltages, the curve increases super-linearly and

then at 5.75 V snaps back (electroforms) leaving the device in the low resistance ON state. The decrease of resistance is permanent although the device can be switched between ON and OFF states repeatedly. The current value after the snap-back for the  $R_S = 100 \Omega$  case, reaches about 180 µA due to the current compliance (with a likely overshoot during snap-back). The electroformation event is effectively instantaneous on the time scale of the source meter response with no intermediate states recorded. The red *I-V* curve which was collected beforehand, does not show a permanent change and can be retraced for decreasing source voltage. The red curve corresponds to  $R_S = 34 \text{ k}\Omega$  (standard ohmic resistors of 33.7 k $\Omega$  chosen for experimental convenience;  $\sim 300 \Omega$  added extracted by calibrating for the resistance of pad and cross-bar traces). At low voltages, it follows the same path as the one for  $R_S = 100 \Omega$  but extends to higher current values without forming. At about 6 V, the I-V trace gradually bends back forming a part of an S-type curve characteristic of current-controlled negative differential resistance (CC-NDR). The presence of CC-NDR usually indicates the presence of an instability that can lead to the spontaneous formation of localized high current density filaments within the device [6]. This phenomenon is characteristic of nonlinear dynamic systems and is often referred to as bifurcation. This also implies that the system will 'snap' to a low resistance state (in this case, the current runaway will result in permanent change of resistance i.e. forming) whenever the total differential resistance becomes negative (equation 2.4). By increasing the source resistance (R<sub>s</sub>), one can limit the range of voltages corresponding to negative total differential resistance (dV<sub>s</sub>/dI) and increase the range accessible to testing. This enables the device to support a stable filament and a corresponding negative differential resistance (dV<sub>D</sub>/dI negative). At sufficiently large  $R_{S}$  the total differential resistance becomes positive (due to  $dV_{RS}/dI$  positive) and the snap can be prevented altogether.

$$V_{S} = V_{D} + V_{R_{S}}$$

$$\frac{dV_{S}}{dI} = \frac{dV_{D}}{dI} + \frac{dV_{R_{S}}}{dI}$$

(2.4)

In other words, if the  $dV_{RS}/dI$  is not large enough (due to small  $R_S$ ), the device will filament instantaneously, as it goes through a snap. The different types of *I-V* in Figure 1 are, therefore, fully consistent with each other and can be explained without invoking any changes of the device structure. In other words, the  $R_S$  enables us to stabilize the pre-forming *I-V* by stabilizing the electronic filament and defines the *I-V* path of the device post-bifurcation. This makes the postbifurcation *I-V* distinct in each case.

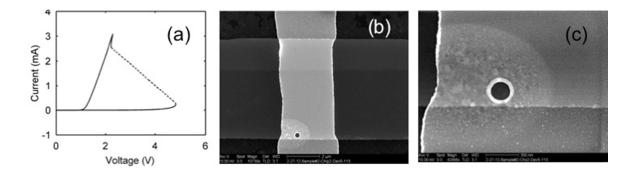

While the data in Fig. 2.4 were obtained on Ta<sub>2</sub>O<sub>5-x</sub>-based devices, we have observed similar behavior in other switching oxides. Figure 2.5 and 2.6 present the results obtained on Pt/TiO<sub>2</sub>/Pt devices. Figure 2.5(a) shows a typical forming *I-V* with the source resistance of 700  $\Omega$ . Initially highly resistive device exhibits forming at 4.7 V with the device formed to high resistance OFF state. The dashed line in the figure corresponds to the load line. The electroformation of TiO<sub>2</sub> devices frequently leads to changes in the top electrode morphology with several groups reporting craters forming at the location of the filament [36],[37]. The changes in the device shown in (a) were imaged by Scanning Electron Microscopy (SEM) using a through-the-lens detector (Figure 2.5(b) and (c)). The low magnification image shows a horizontal stripe corresponding the to bottom electrode and much brighter the vertical top electrode stripe. The most visible feature is the dark dot with a bright edge located in the lower left corner of the active area. The dot is surrounded by a bright "halo". The high magnification image of this feature is shown in Figure 2.5(c). It is quite apparent that the dark dot corresponds to the area

where platinum film delaminated exposing the functional layer underneath. This could be due to either local melting of the metal or solid state diffusion at elevated temperatures. It is widely accepted that such features form at the location of the filament. The "halo" shows a contrast characteristic of polycrystalline grains in a metal. The center portion has grain size of about 100 nm (as measured by an SEM) gradually tapering down to 10 nm toward the edge. We interpret this contrast as the result of Joule heating in a small diameter filament and the resulting grain growth in the Pt electrode. By limiting the current overshoot during electroformation we can eliminate the delamination of Pt but all of out electroformed  $TiO_2$  devices show signs of the halo.

**Fig. 2.5:** (a) Electroforming *I-V* characteristics of the Pt/TiO<sub>2</sub>/Pt 5  $\mu$ m cross-bar device with the source resistance of 700  $\Omega$ . (b) SEM image using through-lens detector of the device after electroforming and (c) a high magnification image of the lower left corner of the same device.

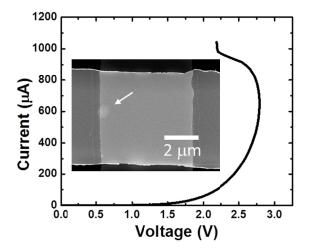

Figure 2.6 shows the I-V characteristics of a similar  $TiO_2$  crossbar obtained with  $R_S = 4.7 \text{ k}\Omega$ . The overall I-V shape is similar to that obtained on  $Ta_2O_{5-x}$  samples with clear CC-NDR behavior and a distinct change of slope in the upper part of the curve at 2 V. In the later part to this report, we interpret such change as due to two different mechanisms contributing to the increase of conductivity with applied bias, namely thermal and electronic. SEM micrograph in the inset shows the contrast of the top electrode after the test. The contrast across the device is uniform with the exception of a bright circular area with the diameter of about 0.7  $\mu$ m located near the left edge of the device. The feature has all characteristics of the halo shown in Fig. 2.5 and is consistent with current constriction to a small diameter filament associated with NDR. The above observations indicate that the voltage and temperature non-linearity is characteristic of most resistive switching oxides.

Fig. 2.6: Negative differential resistance observed in 20 nm thick  $TiO_{2-x}$  cross-bar with  $R_S = 700 \Omega$ . SEM image (inset) shows the evidence of the current constriction in the CC-NDR voltage range.

#### 2.4. Reversibility of Forming Process

Additional insight into the dynamics of the electroformation process and current filamentation was obtained using time domain transmissometry (TDT) (detailed description in the Appendix A). It must be noted that TDT is a technique that enables delivery of high-fidelity voltage pulses to the device and reading off the transmitted voltage pulses and current through the device without any parasitic overshoots. For the pulse forming experiment, we use constant voltage pulses applied across the device and a 100  $\Omega$  resistance connected in series. TDT allows for monitoring the change of voltage across the device and current as a function of time. Identical devices can be formed at a wide range of voltages, with lower voltages requiring longer incubation time before the device undergoes the electroformation [25].

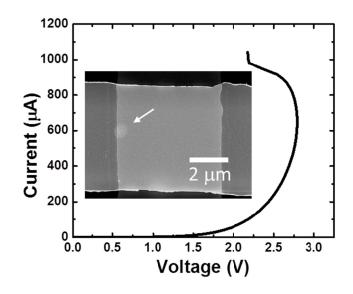

**Fig. 2.7:** Pulsed electroforming experiments. (a) Voltage dynamics obtained by pulsing the device repeatedly (1 through 4) with different pulse durations for the same  $Ta_2O_{5-x}$  device. Large resistance change observed without any permanent change until pulse 4 (b) Similar pulse reversibility experiments on  $TiO_{2-x}$  show morphological changes (shown in (c)) due to higher power dissipation compared to  $Ta_2O_{5-x}$ .

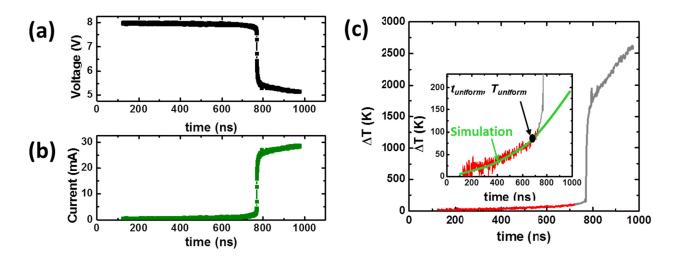

Fig. 2.7(a) shows the voltage across the device as a function of time. Each curve corresponds to the trace during a single voltage pulse applied to the same Ta<sub>2</sub>O<sub>5-x</sub> device. In this experiment, each pulse had the same amplitude but slightly different duration, allowing for the interruption of the process at different stages, a few nanoseconds prior to the completion of forming. As the pulses applied brought about reversible changes (explained below), we were able to use the same device for the entire experiment. The oscilloscope trace started at t = 0 with a fast rise if the voltage due to the leading edge of the applied pulse (not shown). This was followed by a gradual decrease of voltage (initial negative slope) which is associated with decrease of device resistance due to Joule heating. It must be noted here that, while the device has high resistance (~1 M $\Omega$ ) at low biases, it shows a low resistance (~ 5 k $\Omega$ ) at high biases (~ 11 V across the device), following a strong voltage non-linearity (R  $\alpha$  V<sup>-2</sup>), as shown in Figure 2.7(b). This part of the transient can be accurately simulated using known materials parameters and assuming uniform current flow, [discussed in Appendix A for Ta<sub>2</sub>O<sub>5-x</sub>]. The bump at 38 ns is due to a parasitic pulse reflection in the system while the rapid drop between 45 and 55 ns corresponds to the beginning of the electroformation process (and we arrest the pulse at different points, in this range). We assert this based on the magnitude of the resistance change of the device. For example, the device resistance during pulse 4 (green curve in Fig. 2.7(a)) at the onset of the rapid drop is 5 k $\Omega$  and the resistance value at the point of pulse termination is 250  $\Omega$ . This change is too big to be explained by thermal effects in the uniform conduction regime. Moreover, while there was no permanent change of the device resistance after pulses 1-3 terminating before the completion of the process, the device was formed after the pulse 4. The resistance did not recover and remained at the 250  $\Omega$  level after the pulse. The conclusion here is that the rapid drop in resistance in Fig. 2.7(a) does correspond to the electroformation process. The initial part

of the sharp reduction of resistance is volatile and therefore has to be electronic in nature rather than one involving atomic motion.

The results of the similar experiment performed on TiO<sub>2-x</sub> devices are presented in Figure 2.7(b). Each voltage transient and the corresponding SEM image were collected on a different but nominally identical device and each device was exposed to only one pulse. Different devices were used in this experiment for the ease of SEM imaging, while making sure that the incubation time before resistance change (reversible forming, akin to Ta<sub>2</sub>O<sub>5-x</sub>) is the same for all the devices under test. The images show the cross bar-type devices with the light grey vertical strip corresponding to the top electrode and the horizontal darker grey strip corresponding to the bottom electrode. The active area of the devices is the rectangle at the intersection of the electrodes. As in Figure 2.7(a), the pulses were interrupted at various stages of the electroformation process. Traces 1-3 correspond to devices that retained their original resistance after the pulse while trace 4 corresponds to the device on which the electroformation was completed with the permanent drop of resistance. The red trace (1) corresponds to the process interrupted during the uniform current flow stage. The SEM image obtained after this single pulse shows perfectly uniform contrast over the active part of the device. SEM image obtained on the device which experienced the first part of rapid decrease of voltage (trace 2 in Figure 2.7(b) and image 2 in (c)) shows a characteristic halo with diameter of 1.5 µm. The size of the halo on the device which experienced larger resistance decrease (trace 3) increased to 2 µm eventually attaining diameter of 3 µm on the device with permanent resistance change. Such morphological changes on the top electrode are not seen on Ta<sub>2</sub>O<sub>5-x</sub> devices apparently as a result of lower temperature excursions. This observation is a direct evidence of current filamentation

occurring before any permanent changes (such as vacancy accumulation) take place in the memristive devices. This instability is reversible and electronic in nature. Only at its later stages and after the core of the filament reaches high temperatures due to high current density, do the physical changes in the device structure take place. Thus, this experiment relates the electronic filamentation behaviour in the measured oxides to the transient threshold switching seen in chalcogenides (which involves volatile reduction in device resistance (lasting ns to  $\mu$ s), when the device is exposed to short pulses).

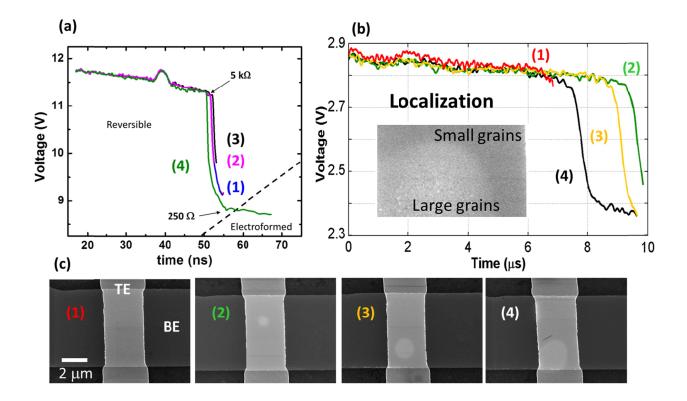

Figure 2.8 (a) shows the experimental set up for measuring the quasi-DC I-V characteristics of 60 nm  $TaO_x$  devices at room temperature. The devices were connected in series with the resistor limiting the current flow with the voltage used in Fig. 2.8 (b) and (c) measured across the device terminals. A clear thermal footprint in form of thermally grown grains of Pt top electrode representing a localized heat affected zone could be observed in these devices (not shown) and has been discussed earlier.

**Fig. 2.8**: (a) Setup used for DC testing of NDR and threshold switching. (b) DC sweep with a ramp rate of 50 V/s exhibiting completely reversible threshold switching in  $I_{device}$ - $V_{device}$  characteristics in a 60 nm TaO<sub>x</sub> device. (c) DC sweep with a ramp rate of 10 V/s showing permanent change in the device characteristics for the same device.

The nucleation model predicts that a prolate ellipsoid shape will produce the lowest energy barrier and will be the fastest to nucleate. The electric field will be locally enhanced at the tips of the spheroid what in turn should provide a positive feed-back for the nucleus growth. This will lead to fast elongation of the nucleus and shunting of the field across the dielectric layer. This behavior results in S-shaped I-V characteristic part of which is observed in Figure 2.8 (b). The device is initially in high resistance (OFF) state with current increasing super-linearly as the function of voltage. At about 6.3 V corresponding to threshold voltage, the device enters into the negative differential resistance portion of the characteristics due to filament nucleation. The I-V rapidly evolves along the load line (upper dashed line in Fig. 2.8 (b) corresponding to  $R_S \sim 700$  $\Omega$ ) to stabilize in a low resistance state at much lower voltage (due to voltage division). The voltage ramp rate in Fig. 2.8 (b) was 50 V/s and was fast enough that when the device arrived at the holding voltage (marked  $V_{h,DC}$  in the figure) it was still in the volatile stage of the filament. At this point, the I-V snapped again along the load line to reach the OFF state at higher voltage. There were no permanent changes to the device and the procedure has been repeated many times. Figure 2.8 (c) shows the I-V characteristics of identical device with a slower ramp-rate (10 V/s). The nucleus has enough time to reach the critical size and the device permanently changes or 'locks-on' to a low resistance state, as indeed observed in Fig. 2.8 (c). One should note that the series resistance used in Fig. 2.8 (c) is much higher than the one used in 2.8 (b).

Whether the NDR-type characteristics are purely a result of heating or supplemented by field dependent conductivity is assessed in the following sections.

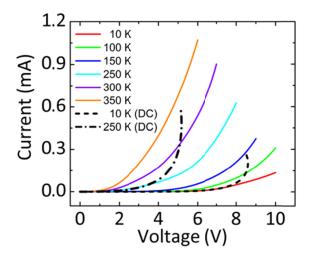

#### 2.5. Voltage Dependent Transient Measurements

The incubation times in  $TiO_x$  and  $TaO_x$  devices were measured by applying a series of rectangular pulses to the device under test and monitoring voltage across the device as a function of time. The duration of pulses was kept constant while their amplitude was gradually increased. For low pulse amplitudes, the voltage across the device slightly drops with time due to decrease of device resistance associated with uniform Joule heating. At certain pulse amplitude, the device undergoes an abrupt reduction in resistance during the pulse, an event that is reflected in a rapid drop of the voltage across the device. This time is defined as the incubation time. The pulse width was determined by the temporal resolution of the oscilloscope. For example, pulse widths for high voltages (> 10 V) were kept constant at 100 ns and the amplitude was changed. After this, the incubation time (which is less than the pulse width) was recorded. Thus, the applied pulse widths were such that the incubation times were contained within the scope trace, without any loss of temporal resolution. The formed state was volatile similarly as happens in chalcogenide-based devices. Each device was used only once as the formation causes permanent change in characteristics.

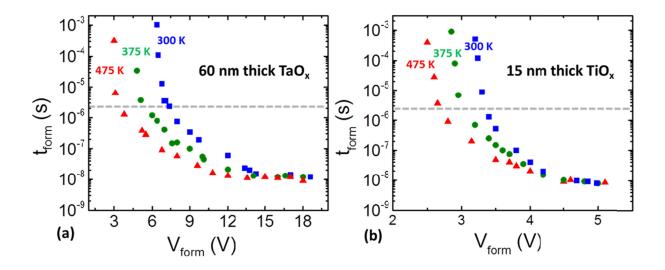

**Fig. 2.9:** Incubation time as a function of applied bias and stage temperature for (a)  $TaO_x$  and (b)  $TiO_x$  based crossbar devices. The horizontal dashed line denotes the value of the thermal time constant of devices with uniform current flow.

This experiment was repeated for pulses of different widths and various stage temperatures. Figures 2.9 (a) and (b) show plots of incubation time as a function of voltage across the device and stage temperature. Each data point represents the average of 5 devices that were subjected to a pulse of the same width and amplitude at the same stage temperature. Both materials exhibit three ranges with different functional dependence of incubation time on applied voltage. At high voltages (> 14 V for TaO<sub>x</sub> and > 4.5 V for TiO<sub>x</sub>), the incubation time is independent of voltage and stage temperature. At intermediate bias, the  $\tau$  decreases with increasing bias and stage temperature. It should be noted here, that the stage temperature is not equal to device temperature as the devices experience considerable Joule heating.

#### 2.6. Temperature, Filament-size and Activation Energy Estimation

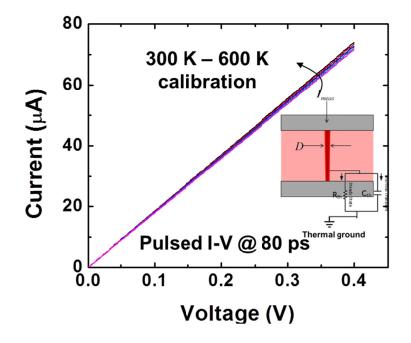

Two procedures allowing for the estimates of the device temperatures have been described in our earlier publications [24],[26] and Appendix A. The first is purely experimental relying on acquiring the I-V characteristics at different stage temperatures using voltage pulses much shorter than the thermal time constant of the device. The accumulated data can be used as a lookup table to extract the temperature of the device with the uniform current flow. The second approach relies on finite element modeling of the temperature increase due to measured power dissipation during the voltage pulse.

For transient measurements, as we are interested in extracting the temperature as the device uniformly heats up (before filament formation takes place), the first method can be used to plot the device temperature as a function of time for every data point in Fig. 2.9 (a) and (b). It was observed that the temperature increases monotonically during the pulse and at the end of the incubation reaches 450 K and 600 K for  $TaO_x$  (60 nm) and  $TiO_x$  (15 nm) devices at the stage temperature of 300 K and highest voltages. Both types of devices reach the maximum of 700 K at the stage temperature of 475 K. At low voltages for which the incubation time exceeds the thermal time constant of our devices [24].[26] (marked with a horizontal dashed lines in Fig. 2.9 (a) and (b)), the dependence on the bias becomes very steep.

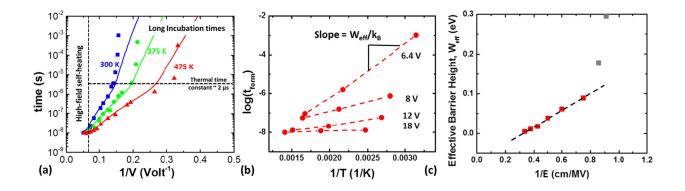

**Fig. 2.10:** (a) Incubation time as a function of 1/V for different stage temperatures. The continuous lines are the results of the nucleation switching model extended to include self-heating effect in the dielectric film. Areas above red dashed line and to the left of blue dashed line delineate regimes of forming where self-heating is important. (b) The Arrhenius plots of  $1/\tau$  versus 1/T. The slopes correspond to effective activation energies at different fields. (c) Plot of activation energy for nucleation as a function of 1/electric field.

Figure 2.10 (a) shows the data from Figure 2.9 (a) plotted as a function of 1/V. It is quite clear that in the intermediate voltage range, the incubation time changes as exp(1/V) in agreement with Eq. (2.3). The slopes of linearly dependent segments are different for different stage temperatures and converge for bias exceeding 14 V. The figure also clearly shows that at low voltages, the dependence on electric field becomes much faster than that predicted by Eq. (2.3). The continuous lines in the figure are the results of the modified nucleation switching model discussed below. Fig. 2.10 (b) presents the data obtained in the intermediate voltage range as a function of 1/T. The values of the temperature T were actual device temperatures at the end of the incubation including the self-heating estimated using the experimental procedure outlined above. In Figure 2.10 (b) for stage temperatures 300 K, 375K, 475K the corresponding actual temperatures reached 325 K, 425 K, 573 K at 6.4V, 363 K, 450 K, 588 K at 8V, 375 K, 485 K, 635 K at 12V, 380 K, 525 K, 683 K at 18V for 60 nm TaO<sub>x</sub> devices. The lines at constant bias are standard Arrhenius plots with slopes corresponding to the activation energy (energy of the

barrier in Fig. 2.1 (a)). It is apparent that the incubation time shows thermally activated behavior with barrier height changing with bias. Figure 2.10 (c) shows the extracted effective barrier height as a function of (1/electric field) and illustrates a strong dependence of nucleation barrier on the electric field. In the intermediate bias regime the dependence is linear in good agreement with Eq. (2.3) which gives the electric field dependent effective barrier height  $W_{eff}$  as  $W_0V_0/V$ .

It is apparent from Fig. 2.10(a) that, with the exception of the high field region, the incubation time depends strongly on both the applied voltage and the device temperature. In the absence of Joule heating and assuming that  $W_0$  and  $V_0$  do not depend on temperature and field, the ratios of slopes of  $ln(\tau)$  vs. 1/V would correspond to inverse of the stage temperature ( $T_{stage}$ ) ratios, which is not the case. To illustrate the origin of this discrepancy, let us consider the intermediate voltage regime at 475 K stage temperature where  $ln(\tau)$  depends linearly on 1/V. Decreasing the voltage between two arbitrary values should increase the height of the barrier and, therefore, increase the incubation time. If we consider the contribution from self-heating, the barrier change would remain the same but the device temperature in the denominator of eq. (2.3) would decrease due to lower dissipated power. It is this change of device temperature that changes the slopes from  $1/T_{stage}$  dependence expected from Eq. (2.3) in Fig. 2.10(a).

The data in Fig. 2.10(a) can be explained fully by Eq. (2.2) if the voltage dependent internal device temperature instead of stage temperature is used. To calculate the temperature T(V) at the nucleation event, we solve the thermal heat balance differential equation in a dielectric film under constant field *E* applied during incubation time  $\tau$ :

$$c_V \frac{\delta T}{\delta t} = J E - \lambda \left( T - T_{\text{stage}} \right)$$

(2.5)

The nucleation event is assumed instantaneous. The temperature T of the nucleus is the same as the temperature of the surrounding dielectric which is higher than the stage temperature  $T_{stage}$ due to current J flowing in the film *before* the nucleation event. The equation (2.5) represents balance of the power components: heat absorption rate in the device (product of temperature increase rate and specific heat  $c_v$ ) with Joule heating power and heat loss rate (product of temperature increase and thermal resistance characterized by the cooling coefficient  $\lambda$ ). The thermal parameters  $c_v = 2.3 \times 10^6$  J/K/m<sup>3</sup> and  $\lambda = 2.2 \times 10^{12}$  J/s/m<sup>3</sup>/K were calibrated by fitting the experimental thermal transient obtained for V = 3.76 V at 475 K stage temperature.

The Joule heating is generated due to the finite current density J flowing in the film. To model the current density J we fitted the pulsed I-V characteristics with the following function [38]:

$$I = JA_d = A_d E \sigma_o \exp\left(-\frac{\Delta E_A}{kT} + \frac{E}{a(T)kT}\right)$$

(2.6)

which is a generic formula used to describe field and temperature activated transport, which we attribute to the field and temperature assisted conduction through existing oxygen vacancies in the film.  $A_d$  is the device area,  $\Delta E_A$  thermal activation energy, E is electric field, and a(T) describes the field dependence of conductance. We found a(T) to be weakly temperature dependent:  $a(T)=1.25 \times 10^9$  V/m/J – (T-300) K x 2.5 x 10<sup>6</sup> V/m/J/K.  $\Delta E_A=0.249$  eV and the film conductivity  $\sigma_0 = 20.9$  S/m. For TiO<sub>x</sub>, while the temperature dependence is the same, the parameters are numerically different.

We solved above equations self-consistently to calculate the electroforming time. We used parameters  $W_0 = 0.65$  eV,  $R_0 = 3$  nm and the high aspect ratio approximation for the oblate nucleus to calculate the effective barrier  $W_{eff}$ . Note that  $W_0$  and  $R_0$  were obtained by fitting the model using Eq. (2.4) to the electroforming data in the intermediate voltage regime at 300 K stage temperature. The prolate nucleus radius is found to shrink from its zero-field value to  $R_{eff} \sim$  1 nm. This is in good agreement with the experimental results in our earlier work [24],[26]. The attempt frequency  $\tau_0 \sim 10$  ns is read off the data in the high field saturation regime in Figure 2.10 (a).

The nucleation switching model with self-heating describes all experimental results in three different regimes and at 3 different ambient temperatures (Fig. 2.10 (a)). At high fields, all three curves level off as the barrier height approaches zero. At intermediate values of bias, the model replicates 1/V dependence with contributions from both the field dependent barrier height and self-hearing. At low voltages, the incubation times exceed the thermal time constant in the film, and the device has enough time to self-heat. In this regime 1/V voltage dependence is therefore strongly enhanced by the field dependence of the internal device temperature.

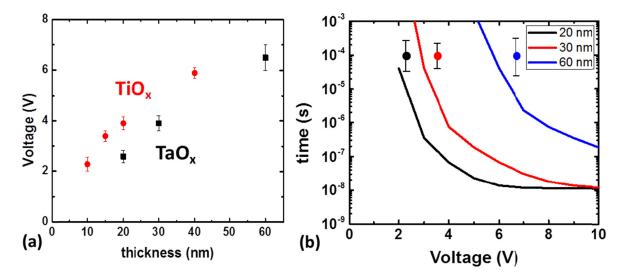

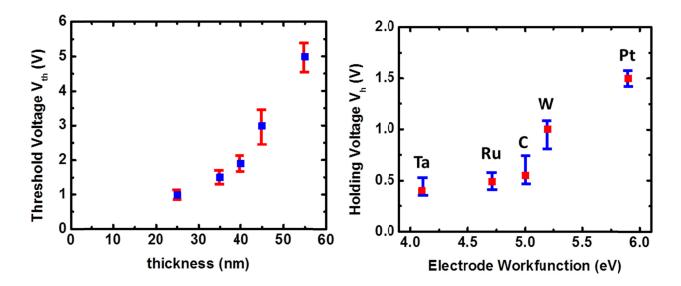

**Fig. 2.11:** (a) Linear increase in the DC /forming voltage as a function of oxide thickness indicating a field-driven forming process. Forming time as a function of applied bias at 300 K stage temperature for 60, 30, and 20 nm  $TaO_x$  films (lines: model, circles: data) in (b). The error bars show distribution over 10 devices.

The nucleation switching model with self-heating was also used to explain another characteristic of the devices, namely the change of the threshold voltage as a function of oxide layer thickness. The experimental data for the threshold voltage values obtained by a quasi-DC sweep for  $TaO_x$ - and  $TiO_x$ -based devices are shown in Fig. 2.11 (a). The voltage scales linearly with the functional layer thickness indicating that a unique field inside the functional layer is needed to form the device. Thus, while there may be some interface effects associated with the forming voltage, the electric field has the most significant effect on the forming. Figure 2.11 (b) shows the calculated incubation times as a function of applied voltage at three values of the oxide layer thickness: 60, 30, and 20 nm. The dots correspond to experimental values in good agreement with the calculated ones. Fig. 2.11 (a) and (b) illustrates that the nucleation switching model with self-heating reproduces the scaling of forming voltage with the film thickness within the data error bars.

However, as the devices undergo NDR, the temperature extraction methodology used in the transient experiments fails. This is because the device no longer conducts uniformly (Appendix A) and needs a self-consistent methodology to estimate the local temperature during the forming process.

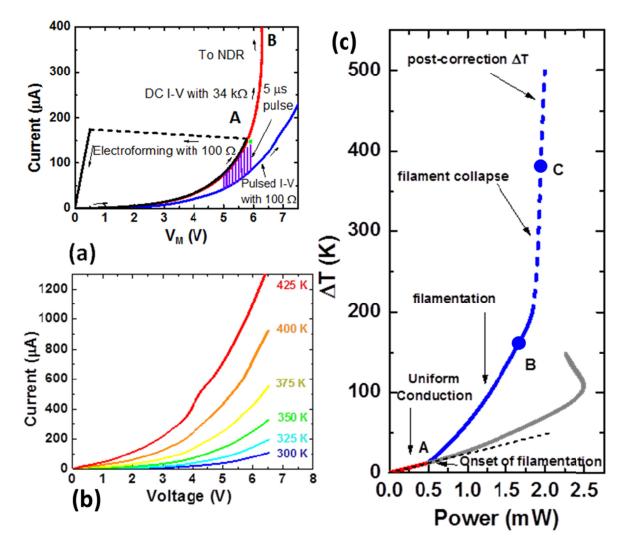

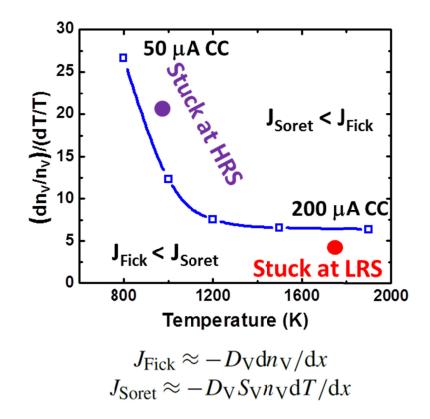

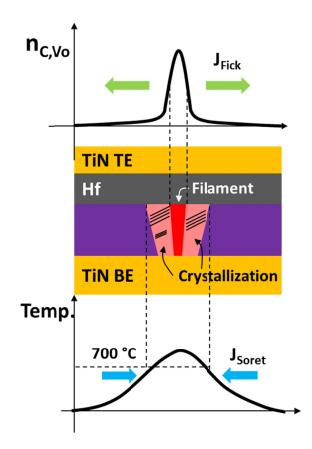

**Figure 2.12:** Temperature and voltage non-linearities as the origin of filamentation. (a) Adiabatic pulsed *I-V* shown in blue taken when the device did not undergo any self-heating. The violet *I-V* dynamic curves connect the initial and the final I vs. T and V vs. T points at 1 ns and 5  $\mu$ s. Electroformation occurs in the 5  $\mu$ s long pulses at the same V, I combination (green spot) as the DC case (black) (b) Adiabatic pulsed *I-V* curve taken as a function of temperature displaying non-linearities in both temperature and voltage. (c)  $\Delta T$  vs. *P* obtained by applying thermometry to the DC *I-V* taken with a 34 k $\Omega$  resistor in series (red, gray curve). Blue curve shows the corrected local temperature. Non-uniform conduction sets in at point A due to thermal non-linearity. Region B represents the thermal onset of filamentation followed by a sharp collapse of the filament due to field/current density dependent instability (Region C).

We will now try to experimentally assess the role of Joule heating in NDR and filament formation. Figure 2.12(a) shows three *I-V* characteristics: the black and red traces are DC I-Vwith  $R_s = 100 \Omega$  and 34 k $\Omega$ , respectively, as shown in Fig. 2.4(a). Since the sweep rate is low, the devices reached thermal steady state at every point (i.e. they heated up). The points on the blue curve were obtained in a pulsed experiment where the current and voltage across the device was measured 1 ns after the pulse leading edge. Since the thermal time constant of our devices was experimentally measured in our earlier work [24][26] to be about 2.5 µs, one can assume that the temperature of the device remained at the stage temperature. It is apparent that excluding the self-heating (blue curve) extended the range of voltages that could be reached without device forming and reduced the current at any given voltage eliminating the CC-NDR. In other words, a device not undergoing self-heating (pulsed I-V), would have a much higher breakdown voltage and current compared to ones that undergo DC forming. Next, we try to experimentally establish the relation between the pulsed I-V and the DC I-V. In addition to three I-V curves, Figure 2.12(a) also shows the results of another series of pulsing experiments represented by almost vertical violet lines. The pulse duration in this experiment was always 5 µs and the violet line corresponds to voltage and current evolution across this 5 µs pulse due to Joule heating. During the pulse, the temperature of the device evolves (Appendix A), approaching the steady state at 5 us. The coincidence of the end points in this experiment and the black trace (DC with the same load resistor) confirm that filamentation and CC-NDR in the low voltage/current range is purely a thermal phenomenon. In other words NDR appears because the device becomes more conductive as it carries more current because of self-heating creating a positive-feedback. Accordingly, the origin of NDR in this part of the I-V characteristics appears to be thermal.

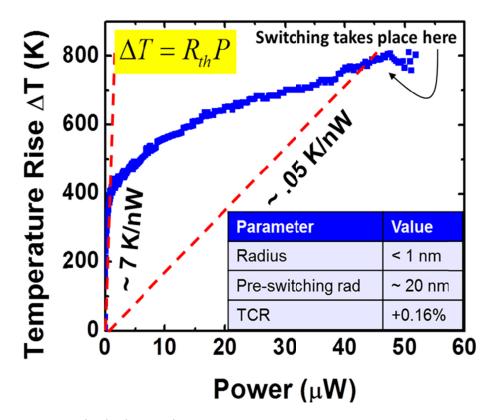

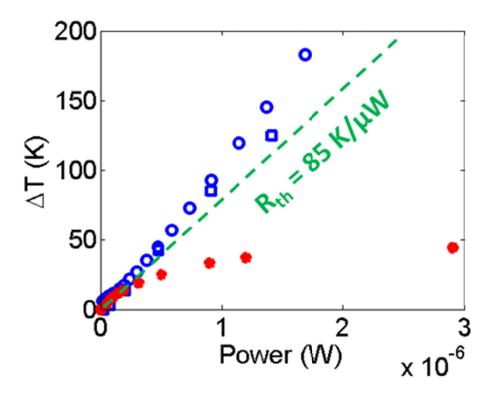

While we have argued that CC-NDR indicates filamentation, it is not clear, at which specific voltage the filament forms or the temperature the local electronic filament reaches before breakdown. We can estimate this by analysis of the dependence of device temperature on dissipated power. For the sake of discussion, let us assume that the current flow is uniform for the entire *I-V* curve obtained with  $R_S = 34 \text{ k}\Omega$  (Fig. 2.4(a)). The device temperature at every voltage was extracted from the pulsed *I-V* measurement calibration as a function of stage temperature, shown in Figure 2.12(b). This data maps the non-linear dependence of current on voltage and temperature and allows the device resistance itself to serve as a thermometer. It must be noted that the pulsed-I-V measurements were taken up to 18 V (not shown here) as the device does not electroform for 5 ns pulses <sup>[41]</sup>. In Figure 2.12(c), we use this thermometry technique to plot the rise in steady-state temperature due to Joule heating during the DC voltage sweep as a function of power dissipated in the device (red trace). The expected rise in temperature should depend linearly on power:

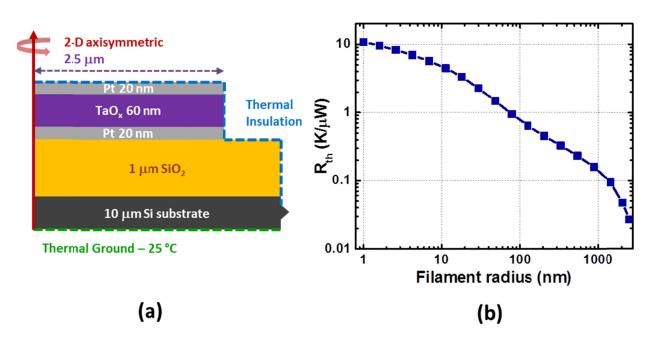

$$\Delta T = R_{th} P \tag{2.7}$$

where,  $\Delta T$  is the rise in temperature in Kelvin,  $R_{th}$  is the thermal resistance seen by the source of heat, and *P* is the power dissipated at the heat source. The thermal resistance, in turn, can be expressed as:

$$R_{th} = \frac{1}{k_{th}} \frac{t}{A}$$

(2.8)

where,  $k_{th}$  is the thermal conductivity of the materials leading to the thermal ground, t is the distance the heat travels to thermal ground and A is the area getting heated up (in steady state) and depends on the filament size. At low voltages, the current flow is uniform and A corresponds to the area of the device. This gives the constant slope of 0.025 K/ $\mu$ W in Fig. 5(c)). This slope corresponds to an  $R_{th}$  which is consistent with the thermal resistance felt by a uniformly conducting 5 µm square device deposited on 1 µm thick SiO<sub>2</sub>. At 600 µW, the  $\Delta T(P)$  slope increases indicating the onset of current constriction (point A in the DC I-V curves). The subsequent section of the curve is gray (at powers above 600 µW) to indicate that the temperature calibration is no longer correct when filamentation sets in; the gray section can only be taken to be a lower bound on the device temperature. As the bias increases further past the onset of filamentation, the slope continues to increase indicating gradual reduction of the filament diameter. The deviation from the initial slope up to 2 mW is attributed to thermallyinduced CC-NDR. Following this, a steep change of slope occurs at higher powers indicating that the mechanism of the non-linearity is completely different from the one that occurs at point A. This region corresponds to the collapse of the filament resulting into a very localized current flow, which we refer to as the electronic filamentation (making a clear distinction in the nonlinearities).

After filamentation onset, the temperature reached is a strong function of filament diameter, with greater current localization leading to higher temperature. Rather than simply postulating a filament size and then estimating the temperature based on that assumption, we have attempted to extract a filament size self-consistently from our data by reconciling temperature rise as estimated from thermal modeling and temperature rise estimated from conductivity change. We

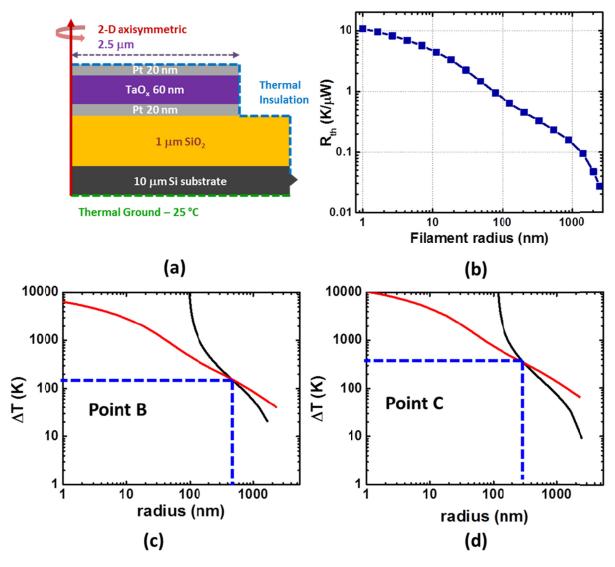

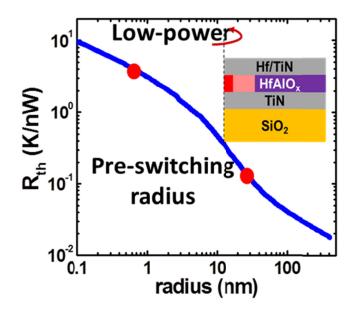

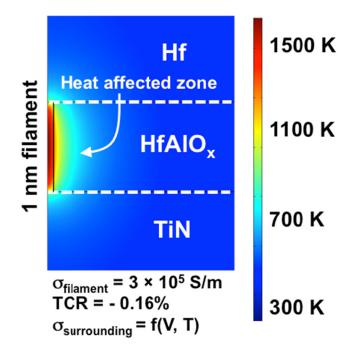

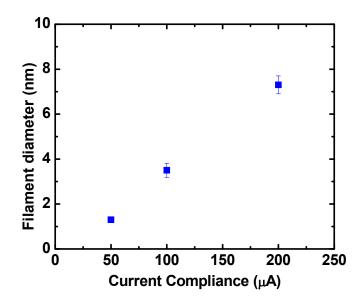

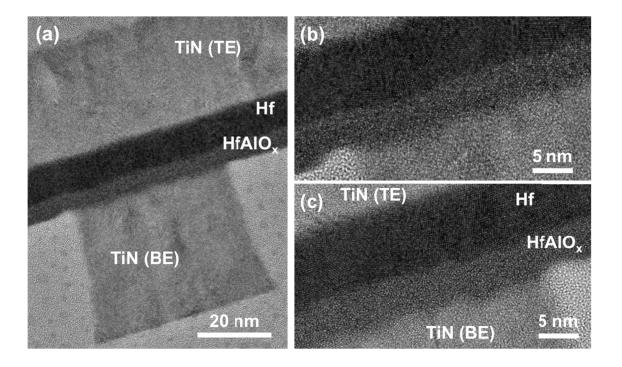

assume, in this case, that the conduction through the filament dissipates power uniformly across the filament. The true temperature is calculated with a self-consistent solution for a filament size under the constraints of simultaneously satisfying the adiabatic *I-V-T* relationship (Figure 2.12(b) with extrapolation as necessary) and the  $R_{th}$  experienced by the same filament size. The adiabatic I-V-T relationship measured with pulsed I-V technique indicates how much power is generated in the device at a given temperature for a combination of current density, J, assuming a filament size. The  $R_{th}$  is a measure of how effective can the generated power be dissipated and is unique to a given filament size. As  $R_{th}$  represents the thermal resistance that is connected between the filament as the heat source and the thermal ground, it can be easily calculated from material properties and a steady state finite element simulation. We use Comsol Multiphysics finite element method solver for the calculation of the  $R_{th}$  as the ratio of the rise in temperature experienced with unit increase in the power dissipated in the filament, at steady state. Figure 2.13 (a) shows the simulation setup used for the solver. The results of the simulation are summarized in Fig. 2.13 (b). From this figure, then, it is possible to estimate the temperature given a filament radius and the measured power dissipated in the device after the onset of the filamentation.

**Fig. 2.13:** True filament temperature extraction. (a) Schematic of the  $Ta_2O_{5-x}$  device used in Comsol Multiphysics electrothermal simulations. (b) Simulated thermal resistance ( $R_{th}$ ) as a function of filament radius. (c) & (d)  $\Delta T$  extracted by parameterizing different radii with (b) – red curve; and using pulsed I-V (black curve) shown at different powers corresponding to points B and C in Figure 2.12(c).

We also know that when we estimate  $\Delta T$  from the pair of *I-V* coordinates, we assume that the current flows through a filament of radius 2.5 µm, i.e. uniform conduction. Thus, for a device undergoing filamentation, we will always underestimate the local filament temperature. Scaling

the current axis in the *I-V-T* thermometer (Figure 2.12(b)) by the ratio of the uniform device area (conduction radius  $r = 2.5 \mu m$ ) and the filament radius, r we get a new range of temperatures for an effectively higher current density. Thus, the corrected curve so constructed is a SECOND, independent figure we can consult to extract a temperature from an assumed filament radius and known I and V measurements. Figures 2.13 (c) and (d) consist of two curves each. The red curves represent the  $\Delta T$  obtained by multiplying the power at points B and C in Figure 2.12(c) with the  $R_{th}$  and parameterizing the radius. The black curves represent the temperature rise predicted by the *pulsed I-V* with parameterized current density for different filament radii. The unique intersection of the two curves is used at each power level to calculate the true filament temperature and radius as the device undergoes electronic constriction of current. Thus, these two constraints are simultaneously applied to the DC measurement to yield the true localized temperature of the device as it undergoes thermal and electronic filamentation. This gives the blue trace (full details of the extraction procedure are explained in the Appendix A). The solid line represents the extraction of temperature made within the experimental limits of the adiabatic I-V-T measurement. The dotted lines indicate the non-linear extrapolation of the measurement data. The non-linear extrapolation was made by assuming a space-charge limited conduction (to which the data matches). It must be noted that the entire NDR curve (up to point C) is reversible and hence we assert the nature of this localization to be electro-thermal and preceding the motion of atoms or vacancies.

Moreover, such deviation is also seen in dynamics measurements in  $TiO_{2-x}$ , (more details in Appendix A for  $Ta_2O_{5-x}$ ). The device temperature can be both measured and simulated till just prior to resistance drop. Temperature rises ranging from 10-150 K have been measured in

devices prior to filamentation in pulse experiments (range refers to the pulse voltage used to form the device, like our previous work [24][26]).

We have presented the experimental evidence of electronic instability in oxide materials commonly used in fabrication of memristive devices. During the approach to the instability, the temperature gradually increases linearly with power to about 320 K. At this point the current flow constricts and the actual temperature of the filament increases faster than uniform current flow calibration. For the Pt/Ta<sub>2</sub>O<sub>5-x</sub>/Pt device discussed in this work, the steady temperature reaches ~500 K as the extracted filament diameter reduces from 5 µm (uniform conduction) to 1 um due to thermal NDR. Additional power produces further filament collapse, and temperature increases rapidly, reasonably estimated as high as 1000 K as the filament diameter collapses to  $\sim$ 10 nm (same as reported by Kwon et al. [19]). The filament diameter estimation has been explained in the supplementary document. These temperatures provide sufficient activation energy to change the oxide in the different ways reported in literature – cause oxygen vacancy creation, crystallization, secondary phase formation[30] and/or melting of the top electrode [19]. The proposed mechanism explains these changes and removes the inconsistency in explaining reduction of the oxide at low temperature. It parallels the mechanism that has been widely accepted in chalcogenide glasses and referred to as "threshold switching" [37],[39]-[41].

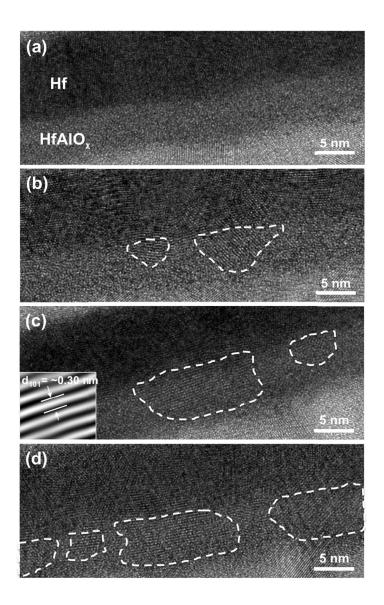

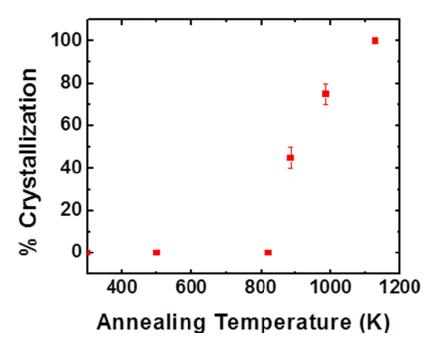

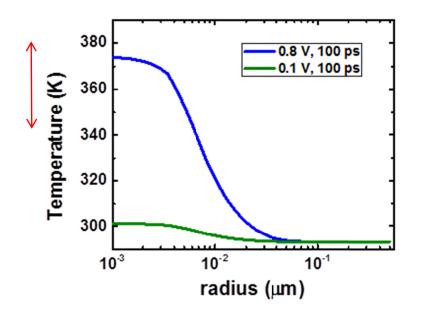

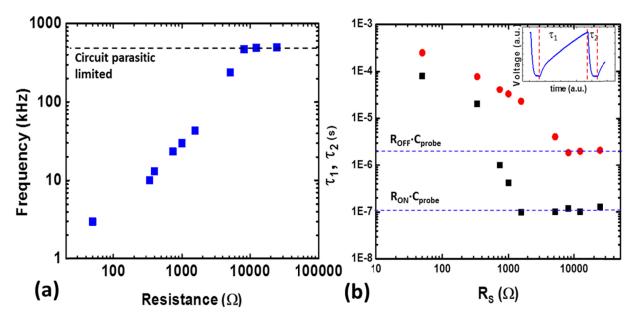

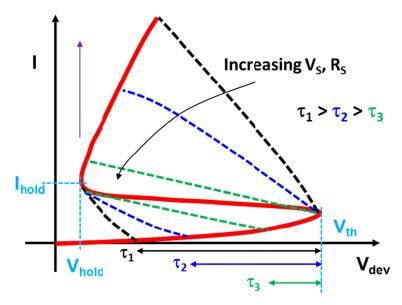

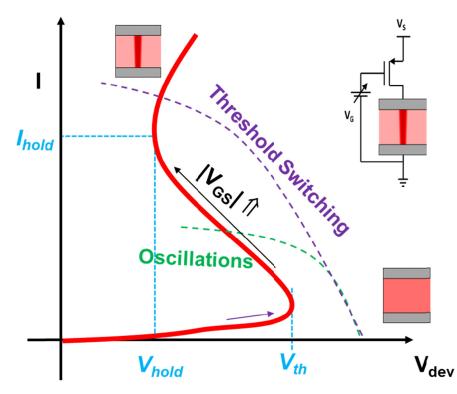

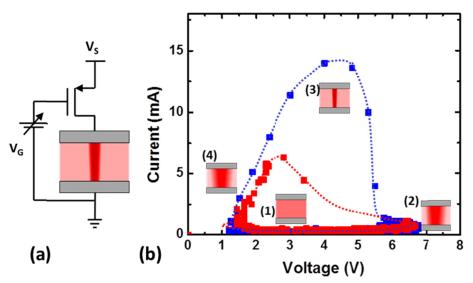

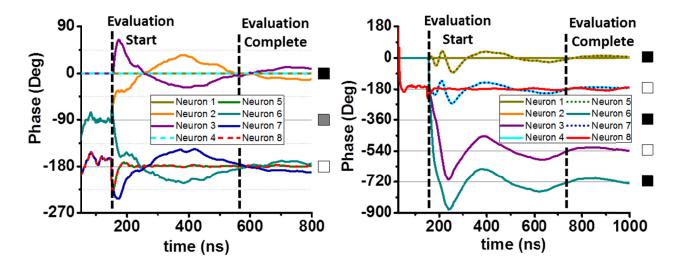

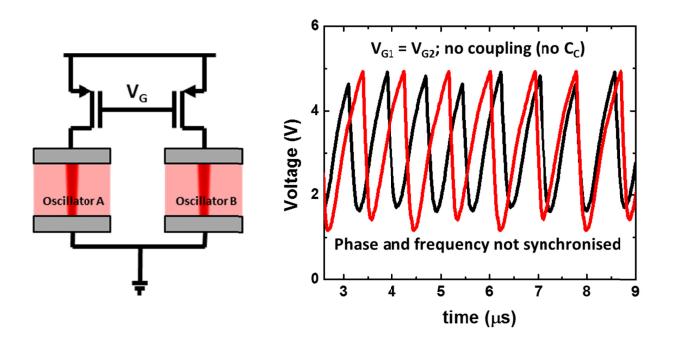

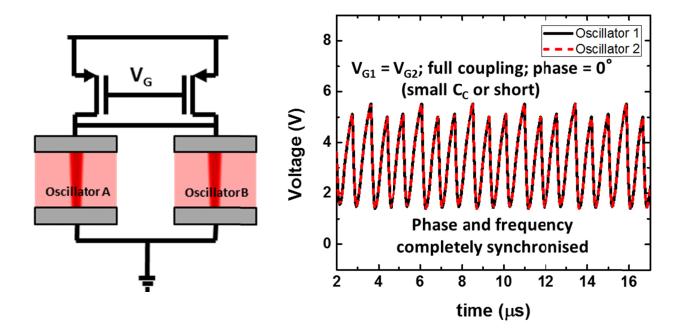

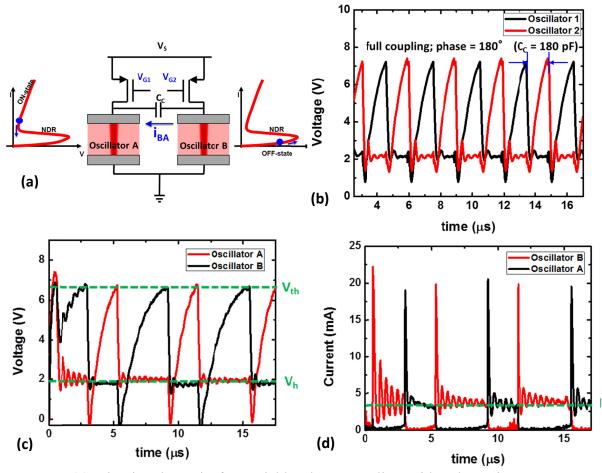

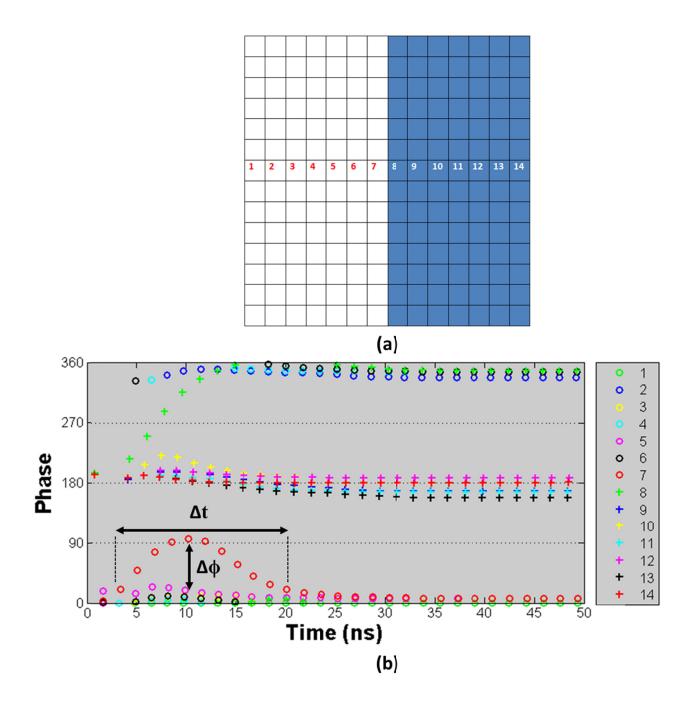

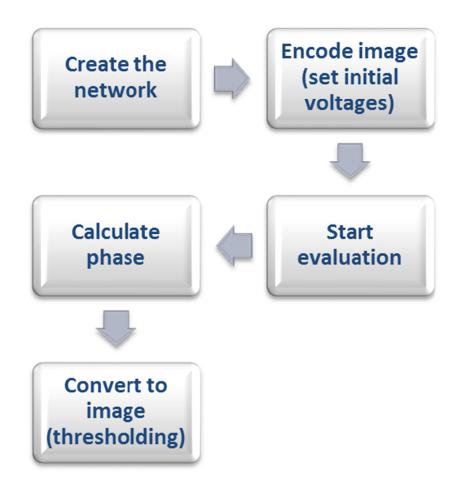

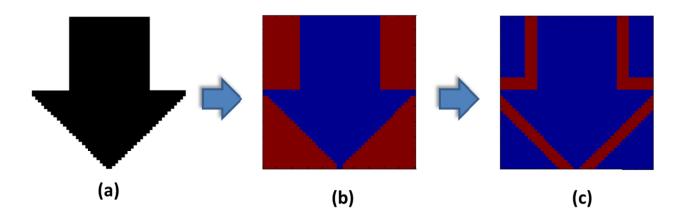

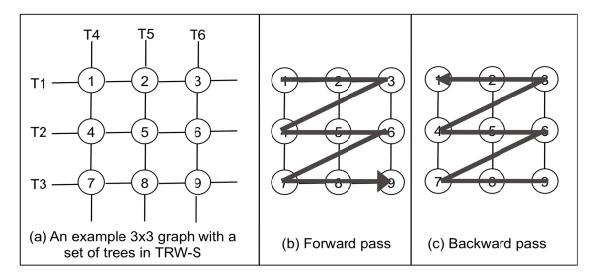

The CC-NDR in metal/oxide/metal structures have been reported number of times in the literature [39]-[41]. Most observations have been made on electroformed devices that already contained a permanent conducting filament. This clearly is only remotely relevant to the discussion of the electroformation process presented here. As noted in the introduction, the model presented in the paper and its experimental evidence agrees with the simulation of the *I-V*