# Lifetime-Aware Task Mapping for Embedded Chip Multiprocessors

Adam S. Hartman December 15, 2015

A Thesis Submitted in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy in Electrical and Computer Engineering Carnegie Mellon University Pittsburgh, Pennsylvania, USA

Copyright © 2015 by Adam S. Hartman. All Rights Reserved.

### Abstract

The International Technology Roadmap for Semiconductors has identified reliability as a growing challenge for users and designers of all types of integrated circuits. In particular, the occurrence of wearout faults is expected to increase exponentially as manufacturing processes scale below 65nm. By acknowledging the importance of these faults and the resulting failures, designers can take steps to improve the expected lifetime of the system. Several system-level techniques, such as communication architecture design and slack allocation, are capable of mitigating the effects of wearout faults and improving system lifetime. Task mapping optimization is another system-level technique that can be applied at both design time and runtime to enhance system lifetime and has several advantages over other lifetime optimization techniques.

The first advantage that task mapping has over other system-level techniques is that it is more flexible. We show that task mapping can positively impact system lifetime in a number of scenarios and does not rely on redundancy or complex reconfiguration mechanisms, although both of those provide additional benefit. The second advantage of using task mapping to improve system lifetime is a lower cost compared to other techniques. Other lifetime improvement techniques seek to augment systems in a cost-effective way to mitigate the effects of wearout faults while task mapping does not necessarily require additional investment in hardware to achieve similar effects. The final, and perhaps most significant, advantage of task mapping is its ability to dynamically manage lifetime as the system is running. While decisions made by other system- and circuit-level techniques must be finalized before the system is manufactured, the task mapping can continue to change to account for the actual state of the system in real time.

We propose two distinct task mapping techniques to be used at the two different times during which optimization can occur. At design time, we take advantage of abundant computational re-

sources to perform an intelligent search of the initial task mapping solution space using ant colony optimization. At runtime, we leverage information from hardware sensors to quickly select good task mappings using a meta-heuristic. Our two techniques can be used together or in isolation depending on the use case and design requirements of the system.

This thesis makes the following intellectual contributions:

- Lifetime-aware design-time task mapping Ours is the first approach to search for initial task mappings that directly optimize system lifetime rather than optimizing other metrics which only influence system lifetime, like temperature and power. Because this technique is meant for use at design time, we employ a powerful search algorithm called ant colony optimization, which takes advantage of a designer's computational resources to find a near-optimal task mapping. Our lifetime-aware design-time task mapping improves system lifetime by an average of 32.3% compared to a lifetime-agnostic approach across a range of real-world benchmarks.

- Lifetime-aware runtime task mapping Ours is the first approach to dynamically manage the lifetime of embedded chip multiprocessors at runtime through the use of task mapping. By leveraging data from hardware sensors and information about the system state, our meta-heuristic approach is able to find high-quality task mappings which extend system lifetime without performing a costly search of the solution space. Our lifetime-aware runtime task mapping improves system lifetime by an average of 7.1% compared to a runtime temperature-aware task mapping approach, and in the best case, system lifetime was improved by 17.4%. Our approach also improved the amount of time until the first component failure by 14.6% on average and 33.9% in the best case.

- Evaluation of lifetime-aware task mapping We measure the improvement in system lifetime resulting from our task mapping techniques across a range of benchmarks. We also compare our lifetime-aware techniques to others which attempt to indirectly optimize system lifetime to show that direct optimization is the only way to achieve maximum lifetime. For example, we show that task mappings that are near optimal in terms of average initial component temperature can result in a range of system lifetimes that is up to 53.2% of the optimal lifetime; clearly, low temperature does not imply long lifetime.

- Co-optimization of competing lifetime metrics The wide range of use cases for embedded chip multiprocessors means that different systems will have different design goals. We consider how the pertinent measure of lifetime changes in different use cases, and analyze the degree to which these competing lifetime metrics can be co-optimized.

- Best practices for a system lifetime simulator We created a simulator which estimates the lifetime of an embedded chip multiprocessor executing one or more applications. The simulator is detailed enough to capture the effects of various system-level design techniques on lifetime, and thus, it is valuable to the field of lifetime optimization research even outside the context of task mapping.

In summary, lifetime optimization for embedded chip multiprocessors is required so that cuttingedge manufacturing processes can continue to be used for a wide range of systems. Our research mitigates the problem of increasingly common wearout faults by proposing and evaluating a pair of design- and runtime task mapping techniques that enhance system lifetime across a broad range of use cases.

## Acknowledgments

My deepest thanks go to Donald E. Thomas, my academic advisor. Working with Don has been very rewarding, and the things I've learned from him about how to validate ideas and communicate them to others are invaluable. This thesis would not have been possible without his experience, effort, and patience.

Next, I would like to thank the members of my thesis committee: Diana Marculescu, Shawn Blanton, and Jim Holt. The thoughts and suggestions that they shared helped me to polish the ideas I originally shared at my thesis proposal to create this final product.

Thank you to my other reviewer, Nikil Mehta, who provided a number of insightful comments that helped me to improve the quality of this thesis.

I would also like to thank Brett Meyer for his collaboration, friendship, and for being an outstanding sounding board. Working with Brett was motivating and enlightening, and he never failed to provide a thoughtful response to any of the questions I asked him.

There are a number of other former and current graduate students from Carnegie Mellon University who deserve my thanks. Thank you to Peter Milder, Peter Klemperer, Kristen Dorsey, and Gabe Weisz for their daily company at lunch and coffee, which always provided interesting and enjoyable conversation. Further thanks go to the Electrical and Computer Engineering softball team, The Gigahurtz, who I had the pleasure of "managing" for five years. The fact that my past teammates are scattered across the country pursuing a wide range of professions speaks volumes about the quality of the people I was fortunate enough to interact with.

Of all the people I met in Pittsburgh, Caitlin Moyer is the most important. When I went to Pittsburgh to attend graduate school, I never imagined I would end up leaving with a best friend. Now my wife, Caitlin was responsible for keeping me sane as we navigated graduate school together, and for providing unwavering motivation when I sometimes lacked it. Thank you Caitlin, I could not have done this without you.

Finally, I would like to thank my family, and specifically my parents, for their support. My parents, Howard and Cheryl Hartman, have always supported my interests, and that is one of the biggest reasons that I find myself where I am today.

The work in this thesis was supported by the Semiconductor Research Corporation through contract 2008-HJ-1795 and by the National Science Foundation through grant CCF-1116856.

## Contents

| 1 | Intro | oduction                                       | 1  |

|---|-------|------------------------------------------------|----|

|   | 1.1   | Motivation                                     | 1  |

|   | 1.2   | Thesis Overview                                | 3  |

|   | 1.3   | Contributions                                  | 5  |

|   | 1.4   | Organization                                   | 6  |

| 2 | Task  | Mapping and System Lifetime                    | 7  |

|   | 2.1   | System Overview                                | 8  |

|   | 2.2   | Task Mapping Problem Definition and Complexity | 11 |

|   | 2.3   | Definitions of System Lifetime and Slack       | 14 |

|   | 2.4   | Comparing Reactive and Proactive Task Mapping  | 16 |

|   | 2.5   | Advantages of Lifetime-Aware Task Mapping      | 18 |

|   | 2.6   | Summary                                        | 20 |

| 3 | Syst  | em Lifetime Simulator                          | 21 |

|   | 3.1   | Monte Carlo Simulation                         | 22 |

|   |       | 3.1.1 Assumptions                              | 23 |

|   |       | 3.1.2 Sample Evaluation                        | 24 |

|   | 3.2   | Failure Mechanisms                             | 27 |

|   | 3.3   | Wear Update Process                            | 29 |

|   | 3.4   | Task Mapping Process                           | 31 |

|   | 3.5   | Communication Groups                           | 32 |

|   | 3.6   | Routing Communication Between Tasks            | 33 |

|   | 3.7  | Using the System Lifetime Simulator in Practice                             | 35 |

|---|------|-----------------------------------------------------------------------------|----|

|   | 3.8  | Summary                                                                     | 37 |

| 4 | Desi | gn Time Task Mapping Optimization Using Ant Colony Optimization             | 39 |

|   | 4.1  | ACO-Based Task Mapping                                                      | 40 |

|   |      | 4.1.1 Task Mapping Synthesis                                                | 42 |

|   |      | 4.1.2 Task Mapping Scoring                                                  | 43 |

|   |      | 4.1.3 Pheromones                                                            | 44 |

|   | 4.2  | Experimental Setup                                                          | 46 |

|   |      | 4.2.1 Bechmark Descriptions                                                 | 46 |

|   |      | 4.2.2 Benchmark Complexity                                                  | 49 |

|   | 4.3  | Validation of the ACO-based Tasked Mapping Approach                         | 50 |

|   |      | 4.3.1 Description of ACO and SA Variations                                  | 50 |

|   |      | 4.3.2 ACO-based Task Mapping Evaluation                                     | 52 |

|   | 4.4  | The Case for Lifetime-Aware Task Mapping                                    | 56 |

|   |      | 4.4.1 Single Design Point Comparison: CPL1 4-s                              | 56 |

|   |      | 4.4.2 Generalized Comparison                                                | 58 |

|   | 4.5  | Summary                                                                     | 60 |

| 5 | Run  | time Task Mapping Optimization Using a Meta-Heuristic                       | 61 |

|   | 5.1  | Task Mapping Heuristics                                                     | 62 |

|   | 5.2  | Benchmarks                                                                  | 67 |

|   |      | 5.2.1 Single Architecture, Multiple Applications                            | 67 |

|   |      | 5.2.2 Single Application, Multiple Architectures                            | 68 |

|   | 5.3  | Results                                                                     | 70 |

|   |      | 5.3.1 Single Architecture, Multiple Applications                            | 70 |

|   |      | 5.3.2 Single Application, Multiple Architectures                            | 75 |

|   | 5.4  | Summary                                                                     | 76 |

| 6 | Co-o | optimizing Competing Lifetime Metrics                                       | 78 |

|   | 6.1  | Effects of System Utilization and Task Mapping on $t_{sys}$ and $t_{first}$ | 80 |

|   |      |                                                                             |    |

|   | 6.2  | Floorplan-Aware Task Mapping Heuristic                      | 80  |

|---|------|-------------------------------------------------------------|-----|

|   | 6.3  | Creating Task Mapping Approaches                            | 82  |

|   | 6.4  | Benchmarks                                                  | 83  |

|   | 6.5  | Results                                                     | 84  |

|   |      | 6.5.1 Maximizing $t_{sys}$ and $t_{first}$                  | 85  |

|   |      | 6.5.2 Increasing the Number of Pareto-optimal TM Approaches | 87  |

|   |      | 6.5.3 Improvements from Floorplan-based Task Mapping        | 89  |

|   | 6.6  | Summary                                                     | 89  |

| 7 | Rela | ated Work                                                   | 92  |

|   | 7.1  | System Lifetime Simulation                                  | 92  |

|   |      | 7.1.1 Failure Mechanism Modeling                            | 92  |

|   |      | 7.1.2 Power Modeling                                        | 93  |

|   |      | 7.1.3 Floorplanning                                         | 93  |

|   |      | 7.1.4 Condor                                                | 94  |

|   | 7.2  | Ant Colony Optimization                                     | 95  |

|   | 7.3  | Wear Sensors                                                | 95  |

|   | 7.4  | Task Mapping for Non-Lifetime Metrics                       | 95  |

|   |      | 7.4.1 Metrics Unrelated to Lifetime                         | 96  |

|   |      | 7.4.2 Metrics that Indirectly Optimize Lifetime             | 97  |

|   | 7.5  | Task Mapping for Lifetime                                   | 98  |

|   | 7.6  | Other System-Level Lifetime Optimizations                   | 100 |

| 8 | Con  | clusions 1                                                  | 101 |

|   | 8.1  | Summary                                                     | 103 |

|   | 8.2  | Directions for Future Work                                  | 105 |

# **List of Figures**

| 1.1  | Qualitative evaluation of resources for task mapping computation and system infor- |    |

|------|------------------------------------------------------------------------------------|----|

|      | mation over time                                                                   | 4  |

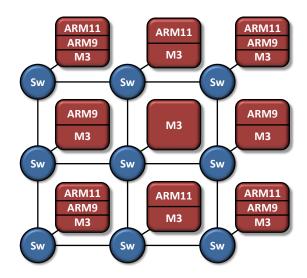

| 2.1  | NoC-based embedded chip multiprocessor system, layered view                        | 9  |

| 2.2  | NoC-based embedded chip multiprocessor system, topological view                    | 10 |

| 2.3  | Graphical representation of $t_{sys}$ and $t_{first}$                              | 15 |

| 2.4  | Comparison of reactive and proactive task mapping in the presence of slack         | 17 |

| 3.1  | System lifetime evaluation process for a single Monte Carlo sample                 | 24 |

| 3.2  | Task mapping wrapper process                                                       | 32 |

| 3.3  | Example of communication groups                                                    | 34 |

| 4.1  | Overview of initial task mapping optimization using ACO                            | 41 |

| 4.2  | Example of task mapping synthesis done by ACO                                      | 43 |

| 4.3  | Example of how pheromones are used in ACO                                          | 46 |

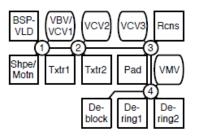

| 4.4  | Multi-window display task graph                                                    | 47 |

| 4.5  | MPEG-4 core profile level 1 decoder task graph                                     | 47 |

| 4.6  | 4 switch communication architecture for the multi-window display application       | 47 |

| 4.7  | 4 switch communication architecture for the CPL1 application                       | 47 |

| 4.8  | 5 switch communication architecture for the CPL1 application                       | 48 |

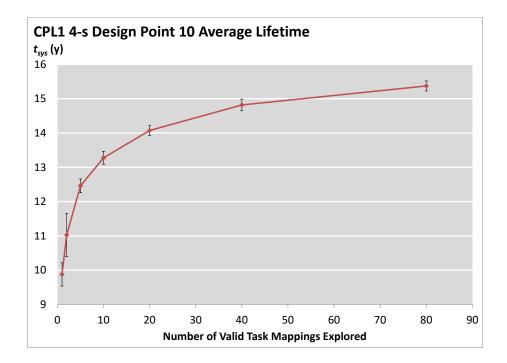

| 4.9  | Comparison of ACO solution quality as the number of valid task mappings is changed | 51 |

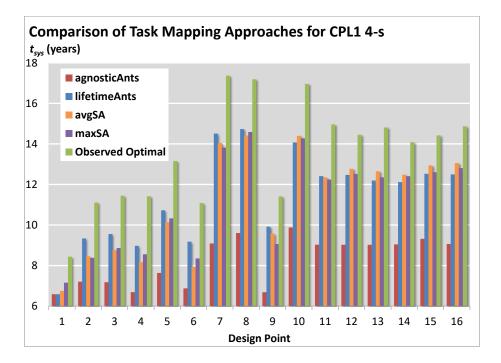

| 4.10 | Comparison of all approaches to observed optimal task mappings for design points   |    |

|      | in the CPL1 4-s benchmark                                                          | 53 |

#### LIST OF FIGURES

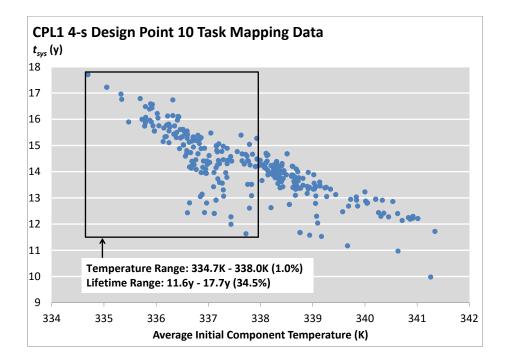

| 4.11 | Average initial component temperature and lifetime data for CPL1 4-s design point            |    |

|------|----------------------------------------------------------------------------------------------|----|

|      | 10 task mappings                                                                             | 57 |

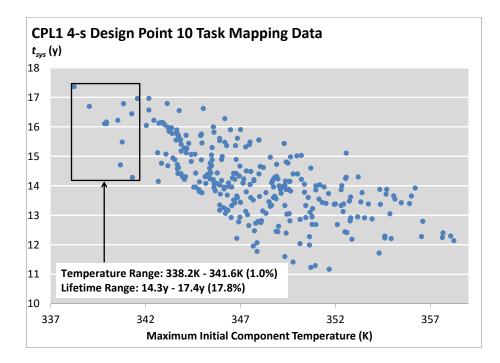

| 4.12 | Maximum initial component temperature and lifetime data for CPL1 4-s design                  |    |

|      | point 10 task mappings                                                                       | 58 |

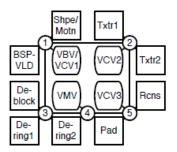

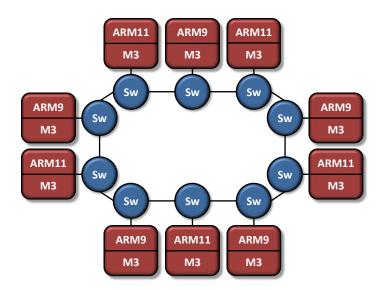

| 5.1  | 9-s mesh hardware architecture                                                               | 68 |

| 5.2  | 10-s ring hardware architecture                                                              | 69 |

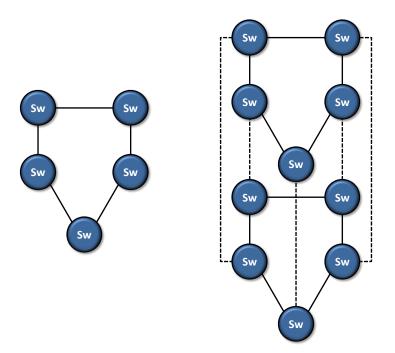

| 5.3  | 5-s ring hardware architectures; left - single, right - double                               | 70 |

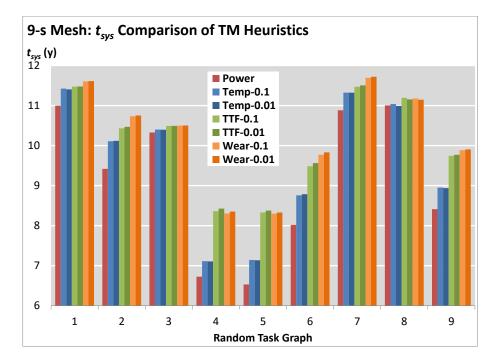

| 5.4  | 9-s mesh $t_{sys}$ results                                                                   | 71 |

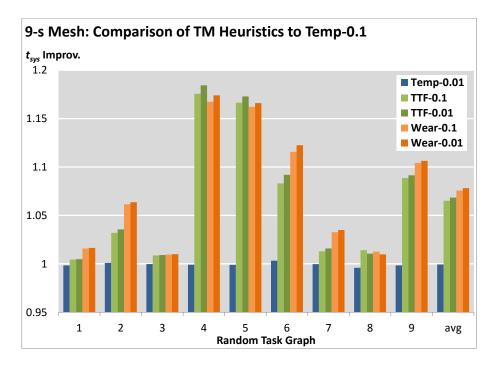

| 5.5  | 9-s mesh $t_{sys}$ improvement                                                               | 72 |

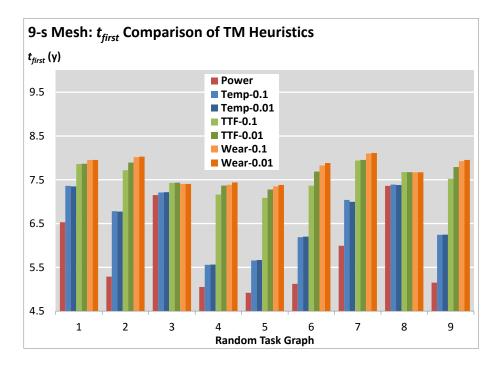

| 5.6  | 9-s mesh $t_{first}$ results                                                                 | 73 |

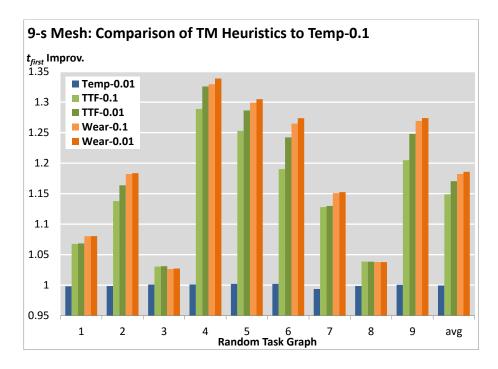

| 5.7  | 9-s mesh $t_{first}$ improvement                                                             | 73 |

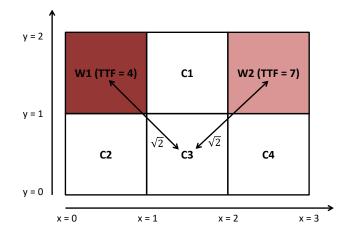

| 6.1  | Example of the floorplan-aware task mapping heuristic                                        | 81 |

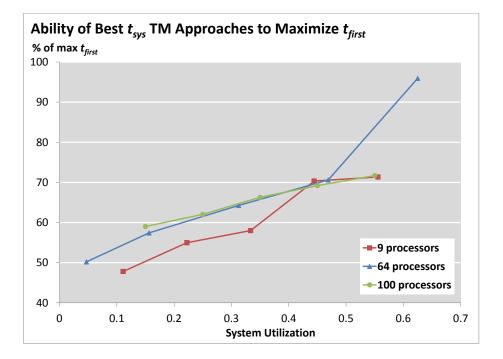

| 6.2  | $t_{first}$ maximization potential using $t_{sys}$ -optimal task mapping approaches          | 85 |

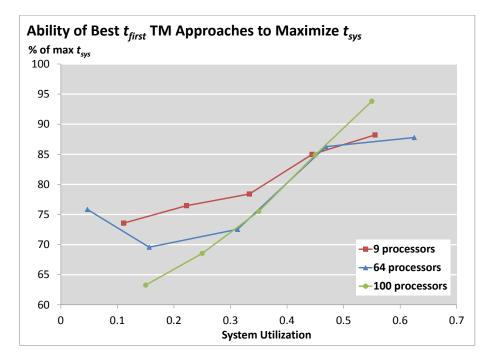

| 6.3  | $t_{sys}$ maximization potential using $t_{first}$ -optimal task mapping approaches $\ldots$ | 86 |

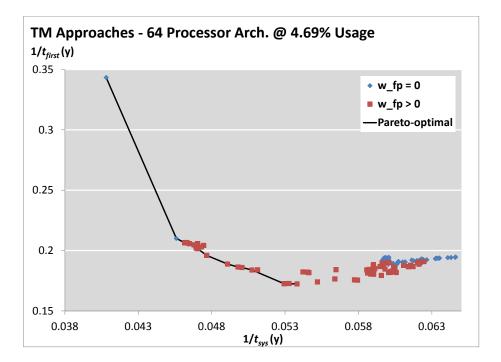

| 6.4  | Results for all task mapping approaches on the 64 processor architecture with task           |    |

|      | graph 1                                                                                      | 88 |

## **List of Tables**

| 2.1 | Summary of the effects of task mapping on system lifetime                       | 18 |

|-----|---------------------------------------------------------------------------------|----|

| 4.1 | Summary of benchmark complexity                                                 | 48 |

| 4.2 | Summary of results for ACO- and SA-based approaches                             | 54 |

| 4.3 | Comparison of lifetime ranges for task mappings with temperature within 1% of   |    |

|     | optimal                                                                         | 59 |

| 5.1 | Task mapping scoring weights used to create task mapping heuristics             | 66 |

| 5.2 | Improvement in $t_{sys}$ by task mapping heuristic and benchmark set $\ldots$ . | 74 |

| 5.3 | Improvement in $t_{first}$ by task mapping heuristic and benchmark set $\ldots$ | 74 |

| 6.1 | Summary of benchmark task graphs                                                | 84 |

| 6.2 | Summary of floorplan-based task mapping heuristic results                       | 90 |

# **List of Algorithms**

| 1 | Communication Routing Algorithm | 36 |

|---|---------------------------------|----|

| 2 | ACO Task Mapping Scoring        | 44 |

| 3 | Task Mapping Algorithm          | 64 |

### **Chapter 1**

## Introduction

#### **1.1** Motivation

Continually shrinking transistor sizes allow integrated circuits to increase in performance and capability while area and power costs are reduced. Both designers and users have relied on these manufacturing process improvements for over 50 years to increase the functionality and usability of new integrated circuits. More recently, the level of integration has risen to a point where multiple processors, memory, their interconnect, and other peripherials can all be implemented in a single package. These packages are small enough in size that they can be used in a vast number of applications. So called embedded chip multiprocessors are integral to cellular phones, cars, home appliances, communications infrastructure, and numerous other areas of technology that we interact with on a daily basis.

However, there are several drawbacks to process improvements, and degradation of system lifetime is one of the most significant. *System lifetime* can be measured as the amount of time between when the system is powered up for the first time and when the system is no longer able to execute its intended application(s). If all other variables are held constant, a system implemented in a process with a smaller geometry will fail sooner than the same system implemented in a process with a larger geometry. The negative effect of decreases in process geometry size on system lifetime is significant enough that the International Technology Roadmap for Semiconductors has specifically identified it as a problem [1].

The cause of system lifetime degradation is well known. As a system operates, the physical

properties of its transistors and wires will deteriorate until some part of the system is no longer able to meet its original timing constraints. A system's functionality can be reduced to an unacceptable level or become wholly incorrect once a timing constraint is violated. When a system fails due to this phenomenon, it is said to have experienced a *wearout fault*. The rate at which wearout faults occur is dependent on manufacturing process parameters, system usage, and operating conditions. Prior research has shown that the occurence of wearout faults increases exponentially as process geometry decreases past 65nm [2]. As state-of-the-art foundries push their manufacturing processes beyond 14nm, the industry is squarely in the position where wearout faults cannot be ignored.

Both producers and consumers of embedded chip multiprocessors will be affected if nothing is done to mitigate wearout faults. At the very least, a wearout fault will cause an interruption in whatever activity the system is performing, and the system will have to be replaced at some cost. There are also scenarios in which the system cannot be replaced, and so system lifetime must meet established goals for a particular product to be usable at all. The perceived quality of the product can be lowered or guarantees made to end users or system integrators may be violated if the system fails sooner than expected.

While the problem of system lifetime degradation has been acknowledged by many, the existing techniques for addressing it have disadvantages. Wearout faults can be mitigated during systemlevel design by adding redundant or over-provisioned computation, memory, and interconnect resources. Such techniques require the designer to make predictions about how the system will age in order to allocate additional resources in a cost effective manner. Another issue with these techniques is that they increase the complexity of the system, which usually results in increased design and verification times. Additional resources may also increase the cost of the system beyond the minimum required to implement the desired functionality.

As an alternative to adding resources at the system level, guardband can be added during circuitlevel design in order to mitigate wearout faults. Adding guardband involves over-engineering specific circuit features (e.g, widening wires beyond their minimum dimensions) in an effort to improve lifetime. The amounts and types of guardband to be added can be prescribed by the foundry based on an internal evaluation of its manufacturing process. Usually, the foundry requires that this guardband be implemented across the entire design for lifetime guarantees to be made, meaning that cost will increase even in locations of the system which do not require additional protection against wearout faults. Perhaps the largest disadvantage of this technique, and also the system-level design technique, is that the runtime characteristics of the system usually cannot be taken into account. As mentioned earlier, system usage impacts the rate of wearout faults, and the benefits of these design-time techniques will be limited by the accuracy of their predictions of system usage. While some systems may be used in a tightly controlled manner, many modern embedded chip multiprocessors experience widely varying workloads in an array of operating conditions.

#### **1.2** Thesis Overview

This thesis addresses the problems described in the previous section by proposing and evaluating two techniques for mitigating wearout faults with lifetime-aware task mapping. Task mapping affects system lifetime since it directly controls the power dissipation of each component in the system, which in turn impacts the temperature of the components and the rate at which wearout faults occur. Our solution is comprised of a design-time technique for finding an initial task mapping and a runtime technique for changing the task mapping as the system operates. The individual techniques are constructed to take advantage of the different types of system information that are available at design time and runtime. Similarly, the design of the techniques accounts for the different sets of computational resources that are available to compute a task mapping at design time and runtime. The main advantages that task mapping has over system- and circuit-level design techniques are that it can be altered at runtime to adapt to variations in the system or workload, and it does not impact the cost of the system as severely.

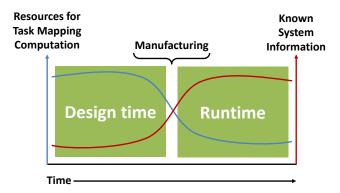

Figure 1.1 shows a qualitative view of how the framing of the task mapping problem changes over time. The x-axis represents time, the red line (right y-axis) represents the amount of known system information, and the blue line (left y-axis) represents the amount of resources available for task mapping computation. A designer may have information about the application(s) to be run on the system at design time, but only sensors in an actual system can provide detailed feedback about how components are accumulating wear. Since the amounts of wear which cause component failure can differ from chip to chip, the quality of the information about the system increases drastically from design time to runtime. What the designer lacks in information at design time can be made up for in computational resources, since it is not unreasonable to assume that a large collection of

Figure 1.1: Qualitative evaluation of resources for task mapping computation and system information over time

servers would be available for design space exploration. In contrast, a running system only has its own computational resources to rely on for configuring itself, and in the case of an embedded chip multiprocessor, those resources may be meager. Manufacturing is shown in the figure as the step between design time and runtime for completeness, but an exploration of manufacturing techniques which improve lifetime is outside the scope of this thesis.

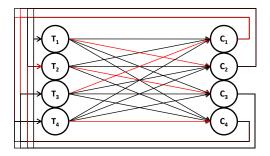

The first element of our solution is a technique for design-time task mapping. Since the task mapping solution space is too large to explore exhaustively, an optimization algorithm is required to approximate the best solution. We use ant colony optimization (ACO) in this context to search for the initial task mapping which results in the longest system lifetime. ACO is a powerful search strategy in which the problem is represented as a graph that is traversed by simulated ants to build candidate solutions. Solution quality is iteratively improved through communication between past and future ants by annotating the graph in a way that echoes the chemical pheromones real ants use to mark paths to food sources. ACO takes advantage of the non-trivial amounts of time and computation resources that are available to an engineer designing a system to find a near-optimal solution for an initial task mapping.

As a system runs, it is likely that the task mapping should be updated to account for variations in the workload and the system itself. While there are less significant resources available to compute a near-optimal task mapping than at design time, there exists a wealth of information about the system that isn't available during the search for an initial task mapping. We use this additional information, in the form of values reported from wear and temperature sensors, to inform a customized metaheuristic which periodically changes the task mapping at runtime. This meta-heuristic is the second element of our solution for mitigating wearout faults and picks up where ACO left off to continue optimizing system lifetime after manufacturing.

We use a system lifetime simulator to evaluate our techniques and compare them to alternative approaches. System lifetime is estimated using statistical models of common types of wearout faults in conjunction with a Monte Carlo simulation. Monte Carlo simulation is required because the specific type of statistical models being used, while accurate, preclude an analytic solution. The simulation compounds the already difficult task mapping problem to create a large solution space where the evaluation of a single solution is computationally expensive. The statistical models are driven by manufacturing process parameters and runtime information about the system being simulated, such as temperature. Arbitrary hardware architectures and streaming application task graphs can be described to the simulator for testing with all relevant task mapping techniques.

This thesis includes comparisons of our proposed techniques to competing approaches. Due to the strong dependence of wearout faults on temperature, it has been suggested that systems which are optimized for temperature will also be optimized for lifetime. We provide a detailed analysis of how well temperature-aware task mapping optimizes for lifetime and vice-versa. Because power dissipation directly impacts temperature, a similar argument can be made about power-aware task mapping being able to optimize lifetime. Our results show that using temperature and power as proxy optimization targets for system lifetime results in task mappings that lead to sub-optimal system lifetime when compared to pure lifetime-aware techniques like the ones we propose.

Lifetime is important in a broad range of applications, including those where system complexity needs to be minimized, and the relevant definition of lifetime can change in these cases. Instead of defining lifetime as the amount of time until the system no longer has sufficient resources to execute its application(s), lifetime may mean the amount of time until a single component in the system fails. This thesis also explores the extent to which these two definitions of lifetime can be co-optimized in the context of our proposed solution. By showing that our techniques positively affect lifetime in these situations, we increase the number of use cases in which they are applicable.

#### **1.3 Contributions**

A summary of the contributions of this thesis is as follows:

- a lifetime-aware design-time task mapping technique based on ACO that takes advantage of computational resources to find near-optimal initial task mappings,

- a lifetime-aware runtime task mapping technique using data from wear and temperature sensors to dynamically manage system lifetime,

- an evaluation of lifetime-aware task mapping using a system lifetime simulator with comparisons to techniques that attempt to optimize lifetime indirectly,

- an exploration of how various definitions of lifetime can be co-optimized in complexityconstrained systems using lifetime-aware task mapping, and

- a detailed simulator that uses Monte Carlo simulation to estimate how design decisions, task mapping in particular, affect the rate of wearout faults in components and impact overall system lifetime.

#### 1.4 Organization

The remainder of this thesis is structured as follows. Chapter 2 discusses background information about the relationships between lifetime, task mapping, temperature, and power along with theory about the benefits of lifetime-aware task mapping. Next, Chapter 3 explains the system lifetime simulator that is used to evaluate our proposed techniques. Then, Chapter 4 details the use of ACO to search for near-optimal initial task mappings. Chapter 5 presents our runtime task mapping meta-heuristic for dynamically managing system lifetime. Chapter 6 explores the co-optimization of different lifetime goals using lifetime-aware task mapping. Chapter 7 provides a discussion of related work and Chapter 8 offers directions for future work and our conclusions.

### Chapter 2

## **Task Mapping and System Lifetime**

Before describing the details of our design-time and runtime task mapping approaches, it is important to understand the theory about why different task mappings can result in different system lifetime. While it may be clear to the reader how adding hardware redundancy to a system architecture or adding guardband during circuit-level design can increase the expected lifetime of a system, the mechanisms through which task mapping affects system lifetime are not as straightforward. The degree to which task mapping affects system lifetime is dependent on many things, including when the task mapping is changed, for what metric the task mapping is optimized, the structure of the system, and even the particular definition of lifetime.

Systems structured as embedded chip multiprocessors are are becoming increasingly prevalent due to the broad range of features they support and the fact that numerous configurations are readily available from intellectual property vendors. A product designer can leverage an existing embedded chip multiprocessor to perform several functions rather than designing an ASIC from scratch or integrating a set of existing ASIC designs. While a fully custom hardware design may have performance and power advantages over an embedded chip multiprocessor, the use of an embedded chip multiprocessor allows for significantly reduced design costs and a faster time-to-market for the product. In fact, the cost and time savings realized when using an embedded chip multiprocessor are so large they they enable some products to be created that would not be economically feasible otherwise. Cellular phones, tablet computers, smart televisions, digital media streaming devices, and automobile "infotainment" systems are examples of high volume products which are built around embedded chip multiprocessors. As with any other integrated circuit being manufactured using a cutting-edge process, lifetime is a concern for embedded chip multiprocessors. Because one of the major advantages of using an embedded chip multiprocessor is their low cost, methods of improving lifetime that have little or no impact on cost are ideal. With that requirement in mind, our work focuses on using task mapping as a way to mitigate wearout faults because it avoids the increased costs associated with over-provisioning at the system and circuit levels. Task mapping controls the amount of work being done by each component and is directly responsible for the power dissipation of each component. Component power dissipation has a strong effect on component temperature, and component temperature has a similarly strong effect on how quickly a component accumulates wear. Thus, task mapping affects the times at which the components in the system fail and, consequently, the overall lifetime of the system. We assert that careful manipulation of the task mapping can significantly improve a system's lifetime.

This chapter begins with an overview of the type of system targeted by our task mapping approaches; namely, embedded chip multiprocessors. Following our definition of an embedded chip multiprocessor, we give a formal definition of the task mapping problem and its complexity. Next, we explain the different ways in which the lifetime of a system can be measured and the concept of slack. The definitions of system lifetime and slack are then used to make a high-level comparison of two general approaches to the task mapping problem. Finally, we discuss the advantages of lifetime-aware task mapping over other task mapping approaches which can theoretically improve system lifetime indirectly.

#### 2.1 System Overview

Embedded chip multiprocessors are single-package systems that contain a collection of individual processors that can communicate with each other directly or through shared memory. While the "embedded" moniker has a broad range of connotations, we mean for it to imply that the system is responsible for executing a pre-defined set of applications and is comprised of processors and memories which tend to be more focused on power-efficiency than performance when compared to the corresponding pieces of a desktop computer. We define a system *component* to be any of the individual processors or memories in the embedded chip multiprocessor. Various mixes of

Figure 2.1: NoC-based embedded chip multiprocessor system, layered view

components with different tradeoffs between performance, power, and cost can be used to optimize the embedded chip multiprocessor for a specific set of applications.

There are several design paradigms that can be used to organize an embedded chip multiprocessor at the top level and allow communication between the components. Historically, these types of systems have been bus-based. In this type of architecture, all components in the system are connected to a central bus, which allows for any pair of components to communicate directly with each other. The central bus in this type of architecture has the following drawbacks: it can be a performance bottleneck, it can act as a single point of failure, it can consume large amounts of power, and it can have a high area overhead resulting in increased system cost.

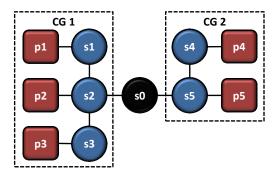

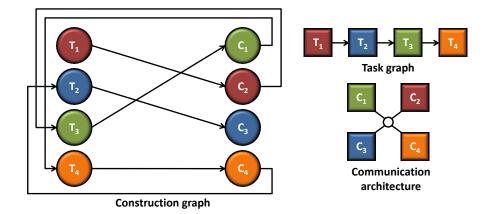

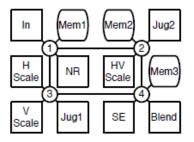

Network-on-chip (NoC) architectures have been introduced as an improvement over bus-based architectures [3]. Components in an NoC send data to each other over a communication architecture that is built with a set of network switches connected in a particular topology. A component can place data on the communication architecture through one of the network switches, and the network switches then forward the data such that it arrives at the desired destination component. NoC architectures improve upon all of the drawbacks of bus-based architectured listed above. NoCs allow for higher performance through a more flexible communication scheme, are more resilient because they can be structured to avoid having a single point of failure, and are more power- and area-efficient because they do not necessarily provide a direct connection between every pair of components in the system. Due to these benefits and industry trends toward the use of these architectures, our work focuses on embedded chip multiprocessors that are implemented as NoCs. Thus, we also consider the network switches that make up the NoC communication architecture to be system components.

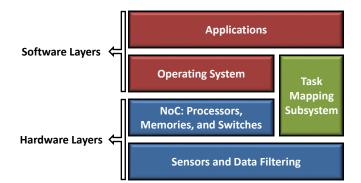

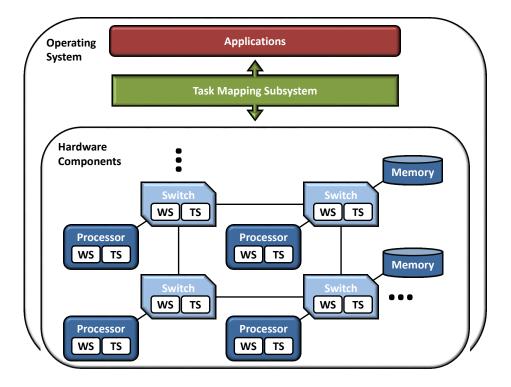

Figure 2.1 shows how a generalized task mapping subsystem fits into the overall design of

Figure 2.2: NoC-based embedded chip multiprocessor system, topological view

an NoC-based embedded chip multiprocessor. The top half of the figure shows software layers (red) while the bottom half of the figure shows hardware layers (blue), and parts of the system which communicate with each other are adjacent. Software layers consist of the applications being executed on the hardware and the operating system which controls the applications' access to the hardware. The upper hardware layer contains the a set of execution resources that are collected in an NoC framework and exposed to the operating system. The lower hardware layer is made up of the temperature and wear sensors inside each of the execution resources and hardware that filters the data from those sensors prior to its output. The task mapping subsystem (green) spans both hardware and software layers since it can be implemented in hardware, software, or a combination of the two. The task mapping subsystem is responsible for collecting information about the applications, through the operating system, and about the hardware, through the sensors, to create a mapping of software tasks to execution resources. Each of the proposed approaches for lifetime-aware task mapping described in Chapters 4 and 5 represents a potential implementation for the task mapping subsystem.

Figure 2.2 shows a topological view of the system described in Figure 2.1. The dark blue boxes

represent processors, the dark blue cylinders represent memories, and the light blue polygons represent switches. Though Figure 2.2 shows four processors and two memories connected by a simple mesh network, our methods are compatible with arbitrary network sizes and topologies. We assume that each processor and each switch has a wear sensor similar to the delay-based design for measuring time-dependent dielectric breakdown in [4]; these are depicted as white boxes labeled "WS" inside those components. Because memories can be protected from failure inexpensively by adding row/column redundancy and a self-repair circuit [5], our work assumes that they cannot fail, and so they have no need for wear sensors. All processors and switches are also fitted with temperature sensors which are represented by the white boxes labeled "TS" inside those components. The wear and temperature sensors are responsible for providing real-time information to the runtime task mapping meta-heuristic described in Chapter 5. Similar to Figure 2.1, Figure 2.2 does not define where the task mapping subsystem is implemented, although it does imply communication with both hardware and software.

#### 2.2 Task Mapping Problem Definition and Complexity

In order for the systems described in the previous section to do any useful work, one or more software applications must be mapped to the processors and memories in the system. Finding solutions to this problem that have a positive impact on system lifetime is the primary purpose of the work presented in this thesis. Once each component has a set of tasks assigned to it, those tasks must be scheduled. We consider task scheduling to be the process of choosing the order in which the set of tasks mapped to a component is executed such that performance constraints are satisfied. Because task scheduling optimization would be applied in addition to task mapping optimization and not in place of it, we assert that the problem is orthogonal to task mapping, and thus, outside the scope of this thesis.

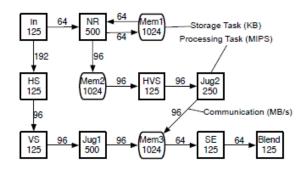

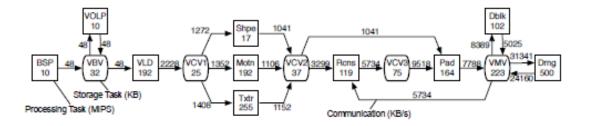

We assume an application is described via a directed graph where each node represents an individual processing or memory task and each edge represents communication between two nodes. The remainder of this thesis refers to these types of graphs as *task graphs*. Processing tasks are synonymous with computational kernels and are annotated with the amount of computational resources, measured in millions of instructions per second (MIPS), they need to meet performance requirements. Memory tasks correspond to data arrays and are annotated with the amount of space, measured in kilobytes (KB), that they will occupy in a physical memory. Edges in the task graph are annotated with the rate, measured in KB/s, at which data is transferred between a source task and a destination task.

A *task mapping* is an assignment of the tasks in a task graph to the components in a system. Given a set of *n* tasks, Equation 2.1 shows that each task has a requirement that is a positive integer. The requirements for both processing and memory tasks, measured in either MIPS or KB, are represented in this single array. Each task requirement is a constant value (i.e., it is not dependent on input data), which means that our formulation only considers streaming applications. Each task also has a type, where type "0" indicates a processing task and type "1" indicates a memory task, as shown by Equation 2.2.

$$req_i \in \mathbb{N} \quad \text{for} \quad i \in \mathbb{N}_{\leq n}$$

$$(2.1)$$

$$tType_i \in \{0,1\}$$

for  $i \in \mathbb{N}_{\leq n}$  (2.2)

A set of m components is represented in a similar way. Equation 2.3 defines a capacity, measured in MIPS for processors and KB for memories, for each component. The type of each component is defined in Equation 2.4 where the 0/1 convention matches that for tasks.

$$cap_j \in \mathbb{N} \quad \text{for} \quad j \in \mathbb{N}_{\leq m}$$

$$(2.3)$$

$$cType_j \in \{0,1\} \quad \text{for} \quad j \in \mathbb{N}_{\le m}$$

$$(2.4)$$

A task mapping which maps a set of n tasks to a set of m components can be described as a matrix in which there is a row for each task and a column for each component. An entry in the matrix will be "1" if the task represented by that entry's row is mapped to the component represented by that entry's column. All other entries in the matrix will be "0". This formulation of a task mapping is shown in Equation 2.5.

$$TM_{ij} \in \{0,1\} \quad \text{for} \quad i \in \mathbb{N}_{\leq n}, j \in \mathbb{N}_{\leq m}$$

$$(2.5)$$

For a task mapping to be considered valid, it must satisfy four constraints. The first two constraints ensure that the task mapping is functionally correct, and the second two constraints ensure that the task mapping meets the performance requirements of the system. We do not require that a task mapping meet any constraints, such as temperature or power, other than the four described below.

First, Equation 2.6 requires that the task mapping be one-to-one, which means that a task may not be split among multiple components, but each component may have multiple tasks mapped to it.

$$\sum_{j=1}^{m} TM_{ij} = 1 \quad \text{for} \quad i \in \mathbb{N}_{\le n}$$

(2.6)

Second, if a task is mapped to a component, then the type of the task must match the type of the component, and this is shown by Equation 2.7.

$$\sum_{j=1}^{m} TM_{ij}(tType_i + cType_j) \in \{0, 2\} \quad \text{for} \quad i \in \mathbb{N}_{\leq n}$$

(2.7)

Third, Equation 2.8 says that the sum of the requirements of all tasks mapped to a component cannot exceed the capacity of that component.

$$\sum_{i=1}^{n} TM_{ij} req_i \le cap_j \quad \text{for} \quad j \in \mathbb{N}_{\le m}$$

(2.8)

Fourth, communication between the tasks must be routed between their host components through the system such that none of the bandwidth capacities of the physical links between components are exceeded. The routing algorithms we describe in Section 3.6 attempt to avoid congestion in the NoC communication fabric when searching for a solution. However, it is possible that we may not be able to find a corresponding routing for a particular task mapping or that a valid routing simply does not exist for some task mappings. If any of the four constraints is violated, the task mapping is considered invalid, and the system will not function when such a task mapping is applied.

Finding a task mapping that is optimal for a given metric (e.g, system lifetime) is an instance of the generalized assignment problem. The generalized assignment problem is a traditional optimization problem that has been shown to be NP-hard, which effectively means that there is no efficient way to locate the optimal solution and that an exhaustive search of the solution space is not feasible for non-trivial problem sizes. The number of ways to map the application(s) to the system increases very quickly with the number of tasks in the application(s) and the number of components in the system. Further, it is computationally expensive to evalute a task mapping with respect to system lifetime as will be shown in Chapter 3.

$$O(|taskMappings|) = procs^{procTasks} * mems^{memTasks}$$

$$(2.9)$$

A bound on the upper limit of the number of task mappings is given by Equation 2.9. In Equation 2.9, *procs* and *mems* represent the number of processors and memories in the system, respectively. The variables *procTasks* and *memTasks* represent the total number of processing tasks and data arrays in the application(s) being mapped to the target system, respectively. Thus, the first term in Equation 2.9 gives the number of ways that the processing tasks can be mapped to processors while the second term gives the number of ways that the data arrays can be mapped to memories. The product of these two terms bounds the number of task mappings for the system as a whole because processing tasks are never mapped to memories and vice-versa. However, not all of the task mappings as counted by Equation 2.9, will be feasible; some of these mappings will violate one or more of the constraints described above. As benchmarks are introduced later in this thesis, we will refer back to this equation and show concrete examples of just how quickly the solution space grows with problem size.

#### 2.3 Definitions of System Lifetime and Slack

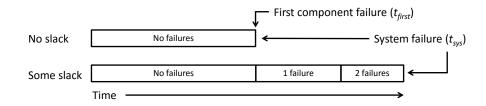

This thesis is primarily concerned with finding task mappings which optimize the system lifetime of the NoC-based embedded chip multiprocessors described in Section 2.1. System lifetime is a general term, and it can be interpreted in several ways depending on the context for which the system has been designed. Two common interpretations of system lifetime, and the ones which are pertinent to this thesis, are *total system lifetime* ( $t_{sys}$ ) and *time to first failure* ( $t_{first}$ ). Definitions of  $t_{sys}$  and  $t_{first}$  are as follows:

- $t_{sys}$  the amount of time between when a system is powered on for the first time and when the system is no longer able to execute its intended application(s) due to component failures.

- $t_{first}$  the amount of time between when a system is powered on for the first time and when the system experiences its first component failure.

Figure 2.3: Graphical representation of  $t_{sys}$  and  $t_{first}$

Both  $t_{sys}$  and  $t_{first}$  are typically measured in terms of years. Chapter 6 provides a more detailed discussion of the different scenarios in which  $t_{sys}$  and  $t_{first}$  are important and why a designer may favor one over the other.

Another principle that requires definition to understand the work presented here is slack. *Slack* is defined as the amount of resources in the system, whether computational or memory, in excess of the minimum amount of resources required to execute the application(s) intended for the system. Computational slack is measured in MIPS and memoy slack is measured in KB. For example, a system is said to have 100 MIPS of computational slack if the combined performance of all processors in the system is 300 MIPS and the applications running on the system require a total of 200 MIPS to meet their performance requirements. Given enough slack, a system may be able to continue to execute its intended application(s) even after one or more components has failed. Existing work [6] has presented a detailed exploration of how slack can be allocated cost-effectively to improve system lifetime. All of the work in this thesis is applicable to systems regardless of how much slack they have, but most of our experiments assume that some slack has been added to the system.

Figure 2.3 shows a graphical representation of  $t_{sys}$  and  $t_{first}$ . The upper bar shows how  $t_{sys}$  and  $t_{first}$  are measured in the case of a system with no slack. The left edge of the bar represents the point in time that the system was first powered on, and time advances to the right of the figure. The section of the bar labeled "No failures" shows the amount of time that the system runs without experiencing a component failure. The right edge of this bar denotes when the first component in this system fails, and therefore also represents  $t_{first}$  for the system. Since the system has no slack, the loss of the first component means that the system as a whole will no longer have the resources required to execute its application(s). Thus, the right edge of the bar also denotes the point in time at which the system fails, or  $t_{sys}$ .

The lower bar in Figure 2.3 shows the same measurements for a system with non-zero slack. In this particular case, the system has enough slack to be able to survive the failure of two components before the remaining components no longer satisfy the performance requirements. Assuming all else is equal, this system runs for the same amount of time without component failures as the system with no slack. The first component fails at the same time it did in the system with no slack, and so the  $t_{first}$  measurements for the two systems are equal. However, this system then continues to run for some amount of time after the first component has failed ("1 failure") and for an additional amount of time after the second component has failed ("2 failures"). A third component will eventually fail and cause the system to fail as a whole, and this is shown as the rightmost edge of the lower bar. In summary, the presence of slack can increase the  $t_{sys}$  of a system but does not necessarily affect  $t_{first}$ .

#### 2.4 Comparing Reactive and Proactive Task Mapping

Another aspect of task mapping which can change the effect it has on system lifetime is the choice about when to compute a new task mapping and apply it to the system. Task mappings can either be computed reactively or proactively depending on the tradeoffs between lifetime and cost being targeted by the designer.

In reactive task mapping, the process of computing a new task mapping is triggered only when a component in the system fails. Because the task mapping is never changed during normal operation in this strategy, there is no performance or downtime penalty incurred due to a change in the task mapping. The need for wear or temperature sensors in a system to inform the task mapping process is obviated when reactive task mapping is employed since the biggest change in the state of the system is the fact that a component failed. Reactive task mapping is the strategy in place for the design time task mapping optimization we describe in Chapter 4.

Proactive task mapping involves the computation of new task mappings at a defined time interval. For example, a new task mapping may be computed and applied to the system every week, every 30 days, every year, etc. The purpose of proactive task mapping is to account for more fine grained changes in system state, such as the accumulation of wear on components, than reactive task mapping is able to consider. One drawback of proactive task mapping is that it may lead to

Figure 2.4: Comparison of reactive and proactive task mapping in the presence of slack

increased hardware costs to enable tasks to be moved as the system is running. Also, proactive task mapping may cause the system to be unusable while the task mapping is being changed, but we believe this issue to be negligible in most cases because of the length of time between remappings that we are proposing and the fact that the remapping schedule could be made to take advantage of system idle time. The notion of proactive task mapping is central to our approach for runtime task mapping optimization that is covered in Chapter 5.

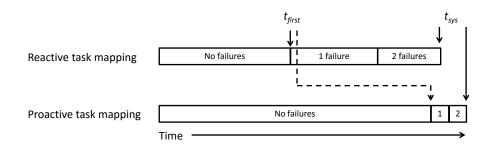

Figure 2.4 shows illustrates the effects of proactive task mapping (lower bar) on  $t_{sys}$  and  $t_{first}$  compared to reactive task mapping (upper bar). In this example, the system has enough slack to surive two component failures. Both bars are divided into three sections which show the amounts of time that the system runs under different numbers of component failures. The most significant change as a result of moving to a proactive task mapping strategy is that  $t_{first}$  increases significantly, and the figure depicts this effect as a longer fraction of time spent in the "No failures" state in the lower bar. The reason for this change is that proactive task mapping is able to take advantage of the slack in the system to delay component failures by distributing the wear being accumulated by the system as a whole across all components. Reactive task mapping, on the other hand, uses the slack in the system only to recover from component failures. Proactive task mapping can have some positive effect on  $t_{sys}$  as depicted by the fact the the lower bar in Figure 2.4 is longer than the upper bar. In theory, proactive task mapping causes all components in a system to accumulate wear almost to the point of failure by the time the first component in the system fails. The system as a whole fails soon after the first component failure since each remaining component is also near failure.

Table 2.1 summarizes the effects of reactive and proactive task mapping on  $t_{sys}$  and  $t_{first}$  in systems with and without slack. All comparisons in the table are done relative to the case where

| Slack Amount                                    | 0                     | > 0       |                |

|-------------------------------------------------|-----------------------|-----------|----------------|

| Lifetime Metric                                 | $t_{sys} = t_{first}$ | $t_{sys}$ | $t_{first}$    |

| Reactive Task Mapping<br>Proactive Task Mapping | baseline<br>+         | +<br>+    | no change<br>+ |

Table 2.1: Summary of the effects of task mapping on system lifetime

reactive task mapping is used in a system with no slack, and so that entry is labeled "baseline". In the case of a system without slack, the entire system will fail as soon as a single component fails, and so  $t_{sys}$  and  $t_{first}$  will always be the same in these cases. Using proactive task mapping even without any slack present allows  $t_{sys}/t_{first}$  to be improved because the task mapping can be adjusted between when the system is first powered on and when the first component fails. When slack is present, reactive task mapping can improve  $t_{sys}$  since it will change the task mapping after each component failure, but it has no effect on  $t_{first}$  since the task mapping is not changed before the first component failure. Proactive task mapping in the presence of slack can improve both  $t_{sys}$  and  $t_{first}$  as was shown in Figure 2.4. The trends shown in Table 2.1 are supported by the data gathered from experiments in Chapters 4 and 5.

#### 2.5 Advantages of Lifetime-Aware Task Mapping

At this point, we have shown the different ways in which task mapping can affect system lifetime, but we have not yet addressed the fact that existing techniques may already mitigate the problem of decreasing system lifetime. Temperature is an important metric to minimize in any system because it will reduce the cost and size of the cooling mechanism required to prevent the system from experiencing thermal failure. In embedded systems, temperature is particularly important because the physical space in which the system operates is typically quite small and allows for little or nothing in the way of active cooling. Several pieces of work in the literature propose temperature-aware techniques, including task mapping, to deal with these problems. Because of the strong dependence of the rate of wearout faults on temperature, it is reasonable to suggest that techniques which optimize system temperature will also optimize system lifetime.

The typical goal of temperature-aware task mapping is to improve system reliability by distributing a workload in time and space to minimize either the peak system temperature or the average system temperature [7]. Other work has discussed temperature-aware thread migration [8] and thread assignment [9]. The authors of [10] present an approach for optimizing the schedule of an embedded application such that system temperature stays within a defined limit. In general, temperature-aware task mappings improve system lifetime, because most, if not all, important failure mechanisms are temperature dependent. As a result, techniques which reduce the temperatures of components in a system also tend to extend component lifetime, and therefore, system lifetime can be extended as well.

However, temperature-aware task mapping fails to capture at least three important classes of factors that also influence system lifetime. The first class of factors involves core properties of the design, such as power density, supply voltage, and circuit geometry. While temperature is primarily related to power density, and many failuire mechanisms are exponentially dependent on temperature, different failure mechanisms are also dependent on a variety of other physical quantities. For example, electromigration is dependent not only on current density, but also circuit geometry. Also, time-dependent dielectric breakdown is dependent on supply voltage, and thermal cycling is dependent on ambient temperature. Further details about these failure mechanisms and how we use them to model system lifetime can be found in Section 3.2. Though many of these parameters change in the same directions as task mappings change because of changes in component utilization (e.g., power density increases as supply voltage or current density increases) they don't change in the same proportion.

The second class of factors deals with system architecture concepts, such as the topology of the communication architecture, the distribution of slack, and the physical floorplan of the system. In systems that allocate execution and storage slack to survive component failure, lifetime is directly related to system architecture. Temperature-aware task mapping is agnostic of which tasks would be the most difficult to remap in the event of a component failure, or alternatively, which components are most important to the longevity of the system. Although there is clearly a relationship between temperature and system architecture via the influence of floorplanning and communication patterns, temperature-aware task mapping does not directly account for these effects. We observe that temperature isn't always a good proxy for lifetime and that temperature-aware task mapping can result in a range of potential lifetimes when optimizing a given temperature metric.

The third class of factors includes those related to manufacutring variability. It is impossible

for all instances of an integrated circuit to be perfectly identical when manufactured on a modern process. Unavoidable die-to-die and chip-to-chip variation mean that each part will have a slightly different set of physical properties, and some of these physical properties will impact how much wear the components in a system can sustain before they fail. But, these changes in physical properties may not lead to measurable differences in temperature, and so the effects of manufacturing variability on system lifetime cannot be captured by temperature-aware optimizations. Instead, task mapping techniques that directly measure component wear and use this information to inform the task mapping decision are required.

Directly optimizing lifetime requires not only that temperatures be generally minimized, but that the inevitable (and at times, advantageous) irregularity in component temperatures be distributed such that the lifetime of important resources is extended at the carefully calculated expense of less important resources. In other words, minimizing a system's peak temperature is important for extending lifetime in general, but system lifetime further depends on the particular component which experiences that peak temperature. Only lifetime-aware task mapping can expose the relationships of both physical parameters and manufacturing variability with component failure, as well as the relationship between component failure and system lifetime, to find task mappings that optimize lifetime. The advantages of lifetime-aware task mapping over temperature-aware task mapping are supported by the experimental data found in Chapters 4 and 5.

#### 2.6 Summary

This chapter summarized many of the foundational concepts for the work in this thesis. We provided definitions of the embedded chip multiprocessors and lifetime metrics that are targeted by our proposed task mapping techniques. We also gave a formal definition of the task mapping problem and its complexity in order to provide context for the choices of algorithms in our proposed approaches. The remainder of this thesis details our approaches for solving the problems defined in this chapter and contains experiments and analyses which serve to illustrate the effects and advantages of lifetime-aware task mapping that are described above.

### Chapter 3

## **System Lifetime Simulator**

In order to evaluate the effects of different task mapping techniques, we need a way to measure the lifetime of a given system to which one or more applications are mapped through a particular task mapping technique. Of course, actually building such systems and observing them until they experince a failure would be both cost and time prohibitive, so we have created a system lifetime simulator. The simulator models the possible sequences of wearout faults that a system can experience over the course of its lifetime. Each sequence of wearout faults will result in a different sequence of component failures, which in turn will result in a different system lifetime. We use Monte Carlo simulation to model sufficiently large subsets of wearout fault sequences and estimate an average value for system lifetime.

The system lifetime simulator explained in this chapter is common to all of our experiments in the remainder of this thesis. There is no inherent bias toward a particular task mapping techique in the simulator itself, so it serves as a platform that allows for meaningful comparisons of task mapping approaches relative to each other. Further, the simulator is detailed enough to capture the effects of a broad range of system-level optimization techniques, which speaks for its utility in the field of lifetime optimization research outside the context of this thesis. While the absolute accuracy of the simulator cannot be validated against actual hardware without significant time and resources, we have taken steps to ensure that it produces reasonable results. Prior work has validated the models for wearout faults, temperature, and power that are used in our simulator, and various parts of our simulator have been calibrated such that inputs to those models match published values for similar systems. Given correct models and correct inputs to those models, we assert that our simulator has sufficient relative accuracy to compare the effects of different task mapping approaches on system lifetime. Additionally, the data presented in the following chapters imply that the simulator is self-consistent in several ways (e.g, a system with more slack tends to have longer lifetime than a system with less slack when all other things are equal).

The remainder of this chapter will explain use the of Monte Carlo simulation, the failure mechanisms that are modeled by the simulator, how the accumulation of wear on components due to those failure mechanisms is tracked, how different task mapping approaches are plugged into the simulator, the technique used to route communication between tasks, and how the simulator can be used in practice. The work described in this chapter was presented in part in [11], [12], and [6].

#### 3.1 Monte Carlo Simulation

Occurrences of the types of wearout faults addressed by our task mapping approaches cannot be directly predicted by any mathematical equation, and instead, are better represented as statistical distributions. Without a direct way of computing the exact points in time at which wearout faults occur for a given system, it is impossible to directly compute the expected lifetime for that system. Thus, we need to use an some indirect method that estimates system lifetime given a set of statistical distributions which describe the wearout faults.

Monte Carlo simulation is a generally accepted method for estimating overall properties of a physical system whose parameters are defined by probability distributions. A Monte Carlo simulation is composed of a number of samples in which each sample represents one particular instance of the system being modeled where the parameters have been set by randomly choosing values according to their statistical distributions. Defining values for the parameters allows some property of the sample system to be measured. Once a sufficient number of samples systems have been evaluated, the measured values of the property of interest from each sample are averaged together to provide an estimate of the actual value of that property.

The remainder of this section describes the assumptions used in building the system lifetime simulator and details the process we use to measure  $t_{sys}$  and  $t_{first}$  for a sample system.

#### **3.1.1** Assumptions

We must make several assumptions about how components in the system fail and when these failures cause the overall system to fail in order to better define our problem. Individual processors and switches within a system may fail over the course of its lifetime due to wearout faults caused by one of the three failure mechanisms explain in Section 3.2. We do not consider scenarios where the individual memories in a system fail due to wearout faults since architectural techniques are already commonly used to mitigate memory failure. However, a memory may become inaccessible by the rest of the system if the switch to which it was connected fails. While such a memory is still capable of functioning, the fact that no other components can communicate with it means that it is indistinguisable from a memory that failed due to a wearout fault.

We assume that some systems can automatically detect the failure of any component (e.g, using [13]), at which point the operating system signals the task mapping process to begin searching for a solution which does not rely on any failed components. Certain switches may also need to be reconfigured, independently of the task mapping process, when a component fails to avoid attempts to route to failed portions of the communication architecture. While it is feasible to implement these recovery and reconfiguration mechanisms, we recognize that their design and validation cost may not make sense in some applications. For systems which eschew recovery and reconfiguration, our simulator simply halts after the first component failure and reports that time as both  $t_{sys}$  and  $t_{first}$  for the system. It is important to understand that our task mapping approaches do not rely on the presence of recovery and reconfiguration mechanisms to improve system lifetime. But, our task mapping approaches have increased impact in systems that implement recovery and reconfiguration mechanisms to survive component failures and give task mapping a longer amount of time in which to perform optimization.

In addition to this method of computing task mappings reactively when components fail, our task mapping process can also be triggered at pre-defined time intervals in an effort to proactively address system lifetime. In this thesis, we use reactive task mapping to evaluate our design-time task mapping approach in Chapter 4 and proactive task mapping to evaluate our runtime task mapping approach in Chapter 5. Regardless of when it is invoked, the task mapping process is responsible for remapping tasks and data from failed resources to those with slack and re-routing the affected

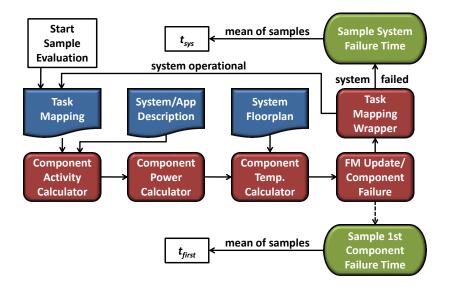

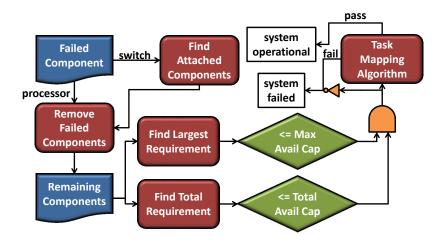

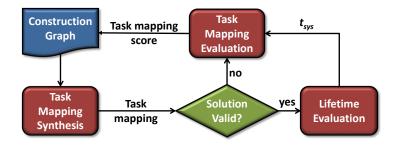

Figure 3.1: System lifetime evaluation process for a single Monte Carlo sample

traffic. We assume that if a valid task mapping exists according to the constraints in Section 2.2, then the system can meet its performance requirements and continue to function. This assumption implies that the operating system is able to create a task scheduling for each component that satisfies the performance requirements of the application(s) given a set of tasks for that component where the sum of the task requirements is less than or equal to the capacity of the component. The problem of finding that task scheduling, and potentially optimizing it for system lifetime, is orthogonal to the work presented in this thesis.

#### **3.1.2 Sample Evaluation**

Figure 3.1 gives an overview of our lifetime evaluation process for a single Monte Carlo sample. First, an initial task mapping is applied to the system. If we are performing design-time task mapping optimization, as in Chapter 4, this initial task mapping is one of those being evaluated by the search. When testing our runtime task mapping optimization, as in Chapter 5, then an initial task mapping which minimizes power dissipation is used for a short time (0.01 years). After this short initial period, the proactive task mapping process is automatically triggered to apply the task mapping approach being tested. This initial task mapping is required in this case because task mapping approaches requiring information from wear or temperature sensors would be impossible to compute when the system is first powered on due to the fact that those sensors do not have valid values at that instant.

Given an initial task mapping, or one that has been computed reactively or proactively, the utilization of each component is calculated based on given information about the system and the application (Component Activity Calculator block in Figure 3.1). Following the notation used in Section 2.2, Equation 3.1 shows how processor and memory utilizations are computed.

$$util_j = \frac{\sum_{i=1}^{n} TM_{ij}req_i}{cap_j} \quad \text{for} \quad j \in \mathbb{N}_{\leq m}$$

(3.1)

According to Equation 3.1, utilization is the ratio of the sum of the requirements of the tasks mapped to that component to the capacity of that component for processors and memories. For a switch, utilization is based on the amount of data passing through the switch, and in order to compute this value, all of the communication between the tasks must be routed to the system's communication network. Details about the process we use to route communication between tasks are described in Section 3.6.

Next, component utilization values are used to calculate the amount of power being dissipated by each component (Component Power Calculator block in Figure 3.1). Processor power dissipation is computed by multiplying the utilization fraction for that processor by the maximum power dissipation for that processor type according to manufacturer data sheets. Our library of processors includes the Cortex-M3, ARM9, and ARM11 architectures created by ARM Ltd. [14]. Memory power dissipation is computed by passing the memory's utilization fraction to CACTI, which is a piece of software which can compute various characteristics of user-defined memory configurations [15]. We assume a library of SRAM memories optimized for low standby power with sizes ranging from 64KB to 2MB. Switch power dissipation is computed by sending the data rate being routed by the switch to ORION, a research tool which models power and performance for interconnect networks [16]. We assume that switches can have a crossbar size of 3x3, 4x4, or 5x5 and that they are equivalent to the Alpha 21364's on-chip router. All processors, memories, and switches are assumed to be implemented in a 90nm manufacturing process. Finally, when a processor or switch has zero utilization, we assume that it switches to a low power state where its power dissipation was 1/3 of its maximum power dissipation.

Component power dissipation values can be used to compute steady-state temperatures for each component, but a system floorplan is also required to do this. For each system architecture being tested, we create a floorplan using BloBB [17]. The floorplan and per-component power dissipation data are sent to HotSpot [8], which returns one temperature value for each component in the system (Component Temperature Calculator block in Figure 3.1). HotSpot uses information from the floorplan to create a resistor network which models the ways in which heat can flow in the system. The power dissipation values are applied to this network and the tool can then solve for the temperature of each component. Our temperature modeling assumptions about range and average value are designed to match previously published temperature modeling assumptions for the same types of systems [18]. These component temperatures are then used to shape the failure distribution for each failure mechanism in that component.