### High-Radix Scalable Modular Crossbar Switches

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical and Computer Engineering

### CAGLA CAKIR

B.S., Electronics Engineering, Sabanci University M.S., Electrical and Computer Engineering, Carnegie Mellon University

> Carnegie Mellon University Pittsburgh, PA, USA

> > May 2016

Copyright © 2016 Cagla Cakir

### Abstract

As process technologies have scaled, the increasing number of processor cores and memories on a single die has also driven the need for more complex on-chip interconnection networks. Crossbar switches are primary building blocks in such networks-on-chip, as they can be used as fast single-stage networks or as the core of the router switch in multi-stage networks. While crossbars offer non-blocking, single-hop, all-to-all communication, they tend to scale poorly with the number of nodes due to the latency and energy of the long wires and highradix multiplexor structures needed. In this work, we investigate how to improve crossbar performance, energy-efficiency, and scalability.

To better understand the design space and scaling limitations, we have developed an on chip switch modeling tool calibrated using circuit-level simulations. The tool enables a design space exploration showing how area, power, and performance vary across radix, data width, wire parameters, and circuit implementation. In addition to conventional design options, we examined capacitively coupled low-swing signaling to improve to energy consumption of the I/O wires. This exploration shows that the main bottlenecks are the long I/O wires and the key to improving the performance and efficiency is to minimize the area. Using these insights, we present modular crossbar switches that can perform better at high radices than the monolithic designs. The modular sub-blocks are arranged in a controlled flow-through, pipelined scheme to eliminate global connections and maintain linear performance scaling and high throughput. Modularity also enables energy savings via deactivation of unused I/O wires.

To evaluate our design, we implemented a prototype radix-64 modular crossbar switch testcip in 40nm CMOS bulk process. The testchip operates at 2.38GHz at 1V nominal supply voltage and consumes 1.2W power. It offers 2.2X better throughput and 2.4X better energy-efficiency than published state of the art designs. We further evaluated modular crossbar networks with the proposed crossbar switches using BookSim2, a network on chip evaluation tool. The proposed design achieves more than 90% saturation throughput with an internal speed up of 1.5, supports high data line rates, and offers lower average network latency compared to conventional crossbars. Evaluation results show that modular crossbars are scalable to high-radices while still offering high-performance, energy-efficiency and onehop simplicity.

## Acknowledgements

This thesis wouldn't have been possible without many wonderful people that I have interacted with and learned from during my time at CMU. They didn't only contribute greatly to my thesis and professional growth, but also made Pittsburgh truly my second home.

Ken Mai has been the most amazing and caring advisor that I could ever ask for. His vast technical knowledge, insightfulness, and approachability have made him an irreplaceable mentor, confidant, and a role model. He taught me how to conduct research properly, ask the right questions, and tackle challenges efficiently and creatively. My time as a graduate student has always been a blast, and I owe it to his guidance and continuous support that kept me motivated and feel accomplished.

Oracle labs offered their financial support, a safe haven to escape hot and humid Pittsburgh summers, and a unique opportunity to work with great mentors. I am indebted to Ron Ho for giving me this chance to collaborate closely with him and learn from him. His never ending cool ideas and ability to quickly identify and solve challenges always inspired me to learn more and become a better researcher. Jon Lexau has also been great mentor who made sure I was well taken care of and contributed generously to my testchip design.

My committee members James Hoe and Michael Papamichael were always gracious enough to share their knowledge and extend their support during my time at CMU. Their feedback and guidelines helped me explore new research areas and made this thesis more complete. CMU was a great place to meet and learn from many wonderful teachers. Special thanks to Larry Pileggi for many interesting lectures as well as his continuous support and mentorship.

Judy Bandola, Shelley Phellps, Elaine Lawrence, Samantha Goldstein, and Nathan Snizasky, made sure I always had the best administrative support, encouragement and delightful conversations.

It was a pleasure to work with many great people in our research group including Mark McCartney, Mudit Bhargava, Yu Cai, Eric Menendez, Craig Teegarden, Weinan Ma, Yun Du, Burak Erbagci, Rachel Dondero, Nail Etkin Can Akkaya, Raymond Carley, Onur Kibar, and Prashant Mohan. Their invaluable contributions, help, and feedback for many tapeouts, papers, presentations, and this thesis are greatly appreciated. Special thanks to Mudit Bhargava, who has been generous enough to always guide me, Craig Teegarden, whose camaraderie made my rookie phase in grad school much more enjoyable, Rachel Dondero, without whom work and all-nighters wouldn't be as much fun at all, and Nail Etkin Can Akkaya for always sharing his tea with me.

I have also been lucky enough to have a great circle of close friends at work that might have lengthen our lunch times and increased the frequency of the coffee breaks. Ekin Sümbül, Berkin Akın, and Soner Yaldız have been great friends as well as great colleagues that made my time at CMU priceless. Also deserving a special note are Ömer Özdemir, Meriç İşgenç, Shadi Saberi, Gökçe Keskin, Emre Karagözler, Qiuling Zhu, Mats Forssell, Da-Cheng Juan for making work much more enjoyable.

Many great friends helped me push through graduate school and feel at home in Pittsburgh. Tuğçe Yüksel and Bekir Bediz were the best company during the harshest nights doing research as well as many fun nights. I was also extremely lucky to have Sercan Yıldız by my side during the final steps of thesis writing and job hunting, despite the times we tried to sabotage each other to keep at the same pace. Also notably Kevin Balko, Bilge Yümer, Ersin Yümer, Bülent Arda Gözen, Burçin Şimşek, Loubna El-Abbadi, Mert Terzi, Günay Orbay, Onur Albayrak, and İdil Ulengin made this journey much more memorable. Last but not least, Melis Hazar, my partner-in-crime and 24-hour support mechanism, enriched my life in every possible way and I wouldn't have come out of this journey as who I am today without her.

Finally, I owe everything I accomplished to my family. I am the luckiest person in the world to have such an amazing, loving, and fun family. My parents, Tülay and Zeki Çakır, gave me everything I needed to be where I am today and always encouraged me to be anything I wanted to be. They are the best parents, best friends, and role-models I can ever ask for. My aunt, my older sister, my best friend, Nuray Bahadır, has always been my favorite teacher and always believed in me unconditionally. My grandparents, Endam and Kazım Bahadır, have been my most dedicated cheerleaders. My aunts, uncles and cousins, Güzelay and Ezgi Özdemir, and Ali, Eray, Emel, Özlem, Beliz, Ozan, and Berin Bahadır are my support system and favorite people. None of this would have been possible without my family, so I humbly dedicate this thesis to them.

# Contents

| 1        | Intr | roduct | ion                           | 1  |

|----------|------|--------|-------------------------------|----|

|          | 1.1  | Motiv  | ration                        | 1  |

|          | 1.2  | High-  | Radix Crossbars               | 4  |

|          | 1.3  | Disser | tation Organization           | 6  |

| <b>2</b> | Des  | ign Sp | pace Exploration              | 9  |

|          | 2.1  | Relate | ed Work                       | 10 |

|          | 2.2  | Cross  | bar Architecture              | 11 |

|          |      | 2.2.1  | Floorplanning                 | 12 |

|          |      | 2.2.2  | Area                          | 12 |

|          |      | 2.2.3  | Input Wires                   | 14 |

|          |      | 2.2.4  | Multiplexers and Output Wires | 14 |

|          | 2.3  | Cross  | bar Modeling                  | 17 |

|          |      | 2.3.1  | Design Parameters             | 18 |

|          |      | 2.3.2  | Evaluation Metrics            | 18 |

|          |      | 2.3.3  | Methodology                   | 22 |

|          | 2.4  | Evalu  | ation                         | 23 |

|          |      | 2.4.1  | Sub-multiplexer Radix         | 23 |

|          |      | 2.4.2  | Physical Implementation Style | 26 |

|          |      | 2.4.3  | Wire Pitch                    | 26 |

|   |     | 2.4.4   | Number of Metal Layers                             | 30 |

|---|-----|---------|----------------------------------------------------|----|

|   |     | 2.4.5   | Data Width                                         | 31 |

|   | 2.5 | Summ    | ary                                                | 32 |

| 3 | Low | v Powe  | er Crossbar Circuits                               | 35 |

|   | 3.1 | Low-S   | wing Crossbar Switch Design                        | 36 |

|   |     | 3.1.1   | Capacitively Coupled Wires                         | 36 |

|   |     | 3.1.2   | Capacitively Coupled Input Data Transmitters       | 38 |

|   |     | 3.1.3   | Input Data Receivers                               | 40 |

|   |     | 3.1.4   | Capacitively Coupled Multiplexers                  | 40 |

|   |     | 3.1.5   | Capacitively Coupled Output Multiplexing and Wires | 46 |

|   | 3.2 | 16x16   | Low-Swing Crossbar Implementation                  | 48 |

|   |     | 3.2.1   | Design Optimization                                | 49 |

|   |     | 3.2.2   | Timing Scheme                                      | 50 |

|   |     | 3.2.3   | Evaluation Results and Comparison                  | 52 |

|   |     | 3.2.4   | Radix Scaling                                      | 53 |

|   | 3.3 | Summ    | ary                                                | 53 |

| 4 | Mo  | dular ( | Crossbar Switches                                  | 57 |

|   | 4.1 | Desigr  | Optimization and Radix Scaling                     | 57 |

|   | 4.2 | Modul   | lar Switches                                       | 60 |

|   |     | 4.2.1   | Modularity                                         | 61 |

|   |     | 4.2.2   | Performance Scaling                                | 65 |

|   |     | 4.2.3   | Energy Savings                                     | 66 |

|   | 4.3 | Switch  | 1 Core Evaluation                                  | 66 |

|   |     | 4.3.1   | Experimental Setup                                 | 67 |

|   |     | 4.3.2   | Optimum Block Radix and Datawidth                  | 68 |

|   |     | 4.3.3   | Energy-Delay Product                               | 72 |

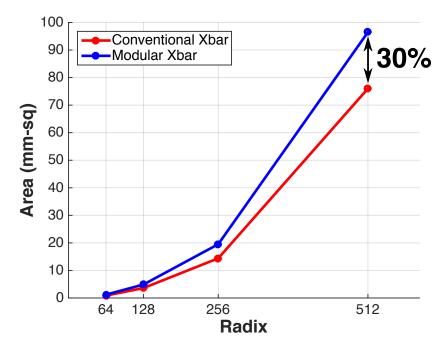

|   |     | 4.3.4   | Area Overhead                                      | 74 |

|          | 4.4                                           | Summary                                          | 75                                                                                       |

|----------|-----------------------------------------------|--------------------------------------------------|------------------------------------------------------------------------------------------|

| <b>5</b> | Mo                                            | dular Crossbar Testchip                          | 77                                                                                       |

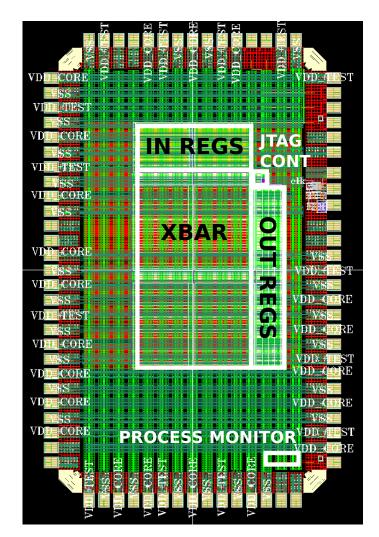

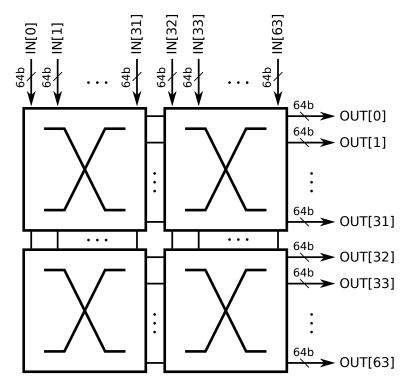

|          | 5.1                                           | Test Chip Overview                               | 79                                                                                       |

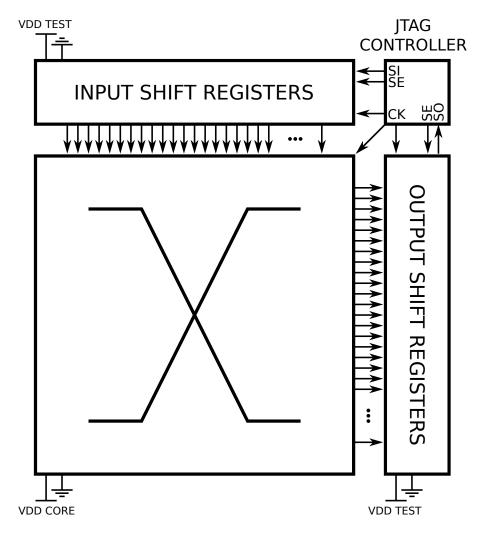

|          | 5.2                                           | Floorplan                                        | 81                                                                                       |

|          | 5.3                                           | Datapath                                         | 83                                                                                       |

|          | 5.4                                           | Control                                          | 88                                                                                       |

|          |                                               | 5.4.1 Example Clocking                           | 92                                                                                       |

|          | 5.5                                           | Test Infrastructure                              | 93                                                                                       |

|          | 5.6                                           | Extracted Simulation Results                     | 95                                                                                       |

|          | 5.7                                           | Summary                                          | 98                                                                                       |

|          |                                               |                                                  |                                                                                          |

| 6        | Mo                                            | dular Crossbar Architecture                      | 101                                                                                      |

| 6        | <b>Mo</b><br>6.1                              | dular Crossbar Architecture         Related Work |                                                                                          |

| 6        |                                               |                                                  |                                                                                          |

| 6        | 6.1                                           | Related Work                                     | 102                                                                                      |

| 6        | 6.1                                           | Related Work       Crossbar Architecture         | 102<br>102                                                                               |

| 6        | 6.1                                           | Related Work                                     | 102<br>102<br>104                                                                        |

| 6        | 6.1                                           | Related Work                                     | <ol> <li>102</li> <li>102</li> <li>104</li> <li>105</li> </ol>                           |

| 6<br>7   | <ul><li>6.1</li><li>6.2</li><li>6.3</li></ul> | Related Work                                     | 102<br>102<br>104<br>105<br>108                                                          |

|          | <ul><li>6.1</li><li>6.2</li><li>6.3</li></ul> | Related Work                                     | <ol> <li>102</li> <li>102</li> <li>104</li> <li>105</li> <li>108</li> <li>113</li> </ol> |

# List of Figures

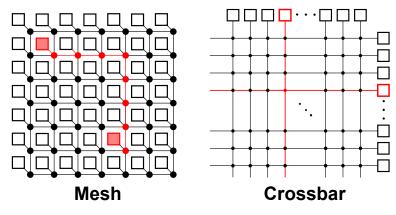

| 1.1  | Mesh and Crossbar Topologies                                                         | 2  |

|------|--------------------------------------------------------------------------------------|----|

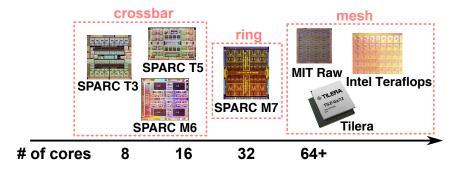

| 1.2  | Networks-on-Chip in Recent Multi-Core Processors                                     | 3  |

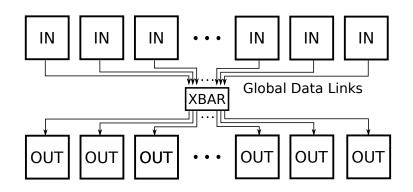

| 1.3  | System view of a crossbar network                                                    | 4  |

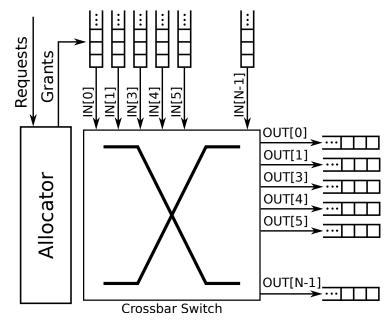

| 1.4  | Crossbar Architecture                                                                | 5  |

| 1.5  | Crossbar switch area depends on radix (quadratically) and the I/O intersec-          |    |

|      | tion width and height                                                                | 6  |

| 2.1  | $N{\bf x}N$ crossbar architecture, where the connection of every input data to an    |    |

|      | output forms an $N:1$ multiplexer                                                    | 11 |

| 2.2  | $N \mathbf{x} N$ crossbar with $DW$ data bits implemented using port-slicing (a) and |    |

|      | bit-slicing (b) floorplans.                                                          | 13 |

| 2.3  | 8:1 multiplexer built using 2:1 sub-multiplexers                                     | 15 |

| 2.4  | (a) Centralized physical implementation of a 8:1 multiplexer                         | 16 |

| 2.5  | (b) Distributed physical implementation of a 8:1 multiplexer. $\ldots$ .             | 16 |

| 2.6  | A static (left) and a dynamic (right) tri-state inverters                            | 17 |

| 2.7  | Floorplan of an $N \times N$ crossbar.                                               | 19 |

| 2.8  | RC modeling of the driver, wire, and receiver for delay calculations                 | 20 |

| 2.9  | Latency of centralized and distributed styles with different sub-multiplexer         |    |

|      | radices                                                                              | 24 |

| 2.10 | Energy of centralized and distributed styles with different sub-multiplexer          |    |

|      | radices                                                                              | 25 |

|      |                                                                                      |    |

| 2.11 | Area of centralized and distributed styles with different sub-multiplexer radices. | 25 |

|------|------------------------------------------------------------------------------------|----|

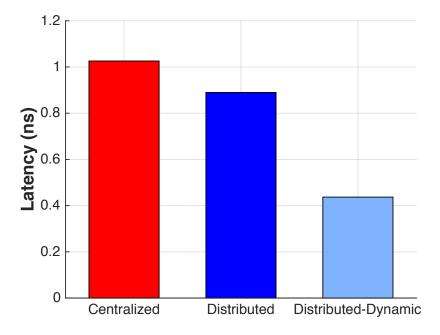

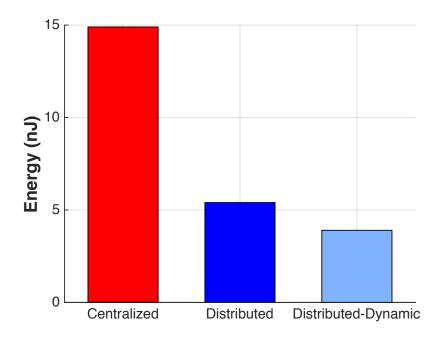

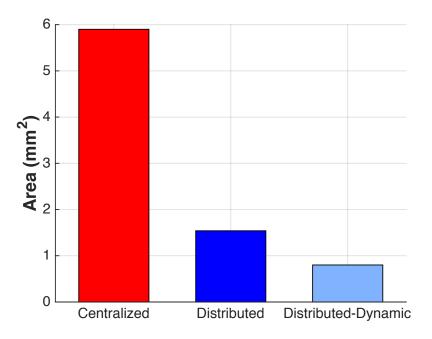

| 2.12 | Latency comparison of of centralized, distributed, and distributed-dynamic         |    |

|      | styles                                                                             | 27 |

| 2.13 | Energy comparison of of centralized, distributed, and distributed-dynamic          |    |

|      | styles                                                                             | 27 |

| 2.14 | Area comparison of of centralized, distributed, and distributed-dynamic styles.    | 28 |

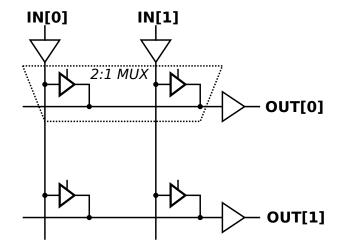

| 2.15 | 2 x 2 1b crossbar architecture with distributed-dynamic multiplexers               | 28 |

| 2.16 | $2 \ge 2$ 1b crossbar circuits                                                     | 29 |

| 2.17 | Delay for different input wire width and spacing                                   | 30 |

| 2.18 | Delay for different output wire width and spacing                                  | 31 |

| 2.19 | Energy-delay product vs number of metal layers                                     | 32 |

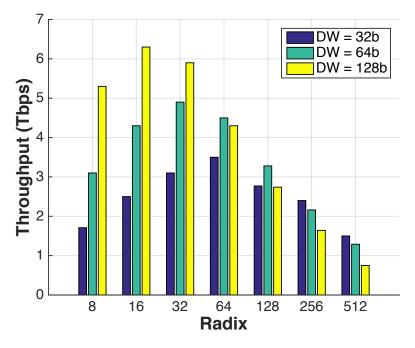

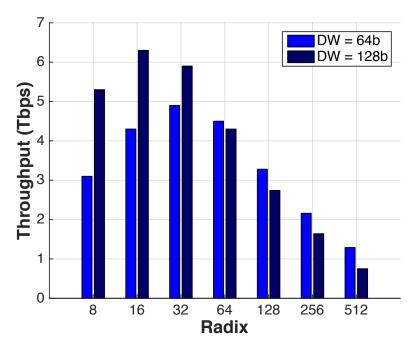

| 2.20 | Throughput for different data widths and radices                                   | 33 |

| 3.1  | A capacitively driven wire scheme.                                                 | 37 |

| 3.2  | Capacitively coupled input data transmitters                                       | 39 |

| 3.3  | The ON capacitance ratio for drain-source connected PMOS                           | 41 |

| 3.4  | The OFF capacitance ratio for drain-source connected PMOS                          | 41 |

| 3.5  | The on to off capacitance ratio for drain-source connected PMOS                    | 42 |

| 3.6  | Capacitively coupled multiplexer                                                   | 43 |

| 3.7  | Latency comparison for radix-8 tri-state multiplexer and capacitively coupled      |    |

|      | multiplexer with a 1mm long output wire                                            | 44 |

| 3.8  | Latency comparison for radix-16 tri-state multiplexer and capacitively cou-        |    |

|      | pled multiplexer with a 1mm long output wire                                       | 44 |

| 3.9  | Latency comparison for radix-32 tri-state multiplexer and capacitively cou-        |    |

|      | pled multiplexer with a 1mm long output wire                                       | 45 |

| 3.10 | Latency comparison for radix-16 tri-state multiplexer and capacitively cou-        |    |

|      | pled multiplexer with a 2mm long output wire                                       | 45 |

| 3.11 | A single switch connection of the capacitively coupled multiplexer                 | 47 |

| 3.12 | Top-level view of the low-swing crossbar design.                                  | 48         |

|------|-----------------------------------------------------------------------------------|------------|

| 3.13 | Timing diagram for the low-swing crossbar design                                  | 51         |

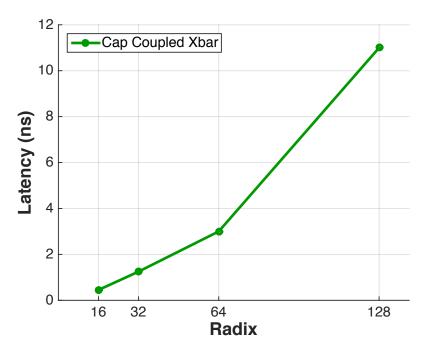

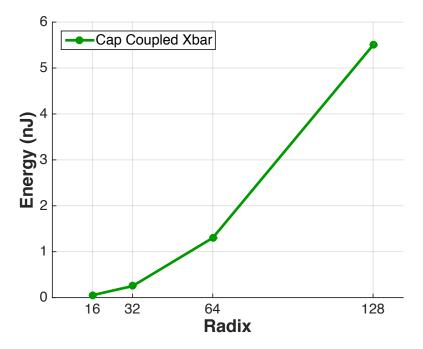

| 3.14 | Low-Swing Crossbar Latency Scaling with Radix                                     | 54         |

| 3.15 | Low-Swing Crossbar Energy Scaling with Radix                                      | 54         |

| 4.1  |                                                                                   | <b>F</b> 0 |

| 4.1  | Crossbar architecture with dynamic tri-state buffers                              | 58         |

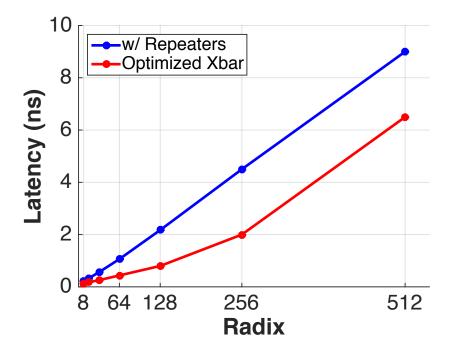

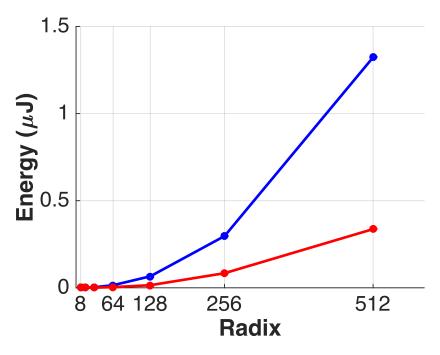

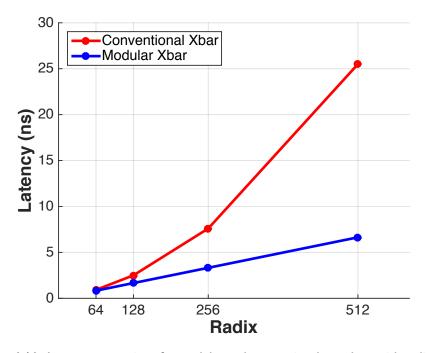

| 4.2  | Latency scaling trends with radix.                                                | 59         |

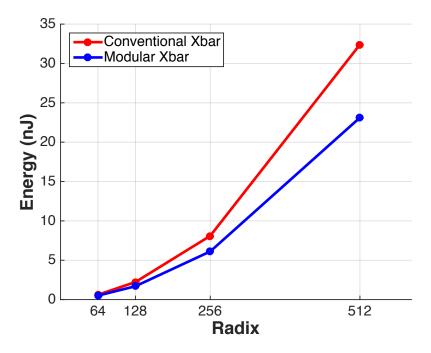

| 4.3  | Energy scaling trends with radix.                                                 | 60         |

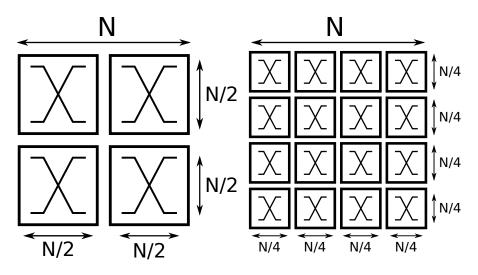

| 4.4  | $N \ge N$ crossbar switch.                                                        | 61         |

| 4.5  | $N\ge N$ modular crossbar switches built with $N/2\ge N/2$ (left) and $N/4\ge$    |            |

|      | N/4 (right) blocks                                                                | 62         |

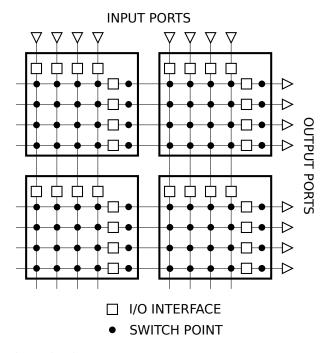

| 4.6  | An 8 x 8 modular switch built using 4 blocks of 4 x 4 blocks. $\ldots$            | 63         |

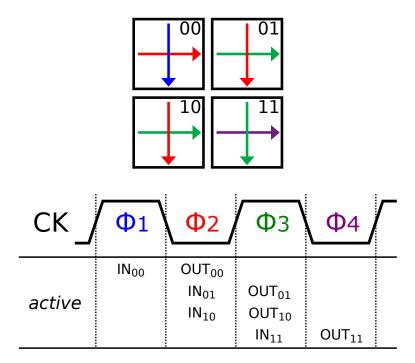

| 4.7  | Clocking scheme for a modular crossbar with 4 blocks.                             | 64         |

| 4.8  | Power savings of 8 x 8 modular crossbars built using 4 x 4 (left) and 2 x 2       |            |

|      | (right) switch blocks.                                                            | 67         |

| 4.9  | Throughput scaling with radix for datawidths of 64 and 128 bits                   | 70         |

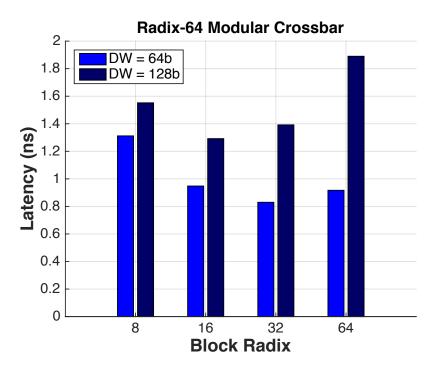

| 4.10 | Single-flit latency for a radix-64 modular crossbar using different block radices |            |

|      | and datawidths.                                                                   | 70         |

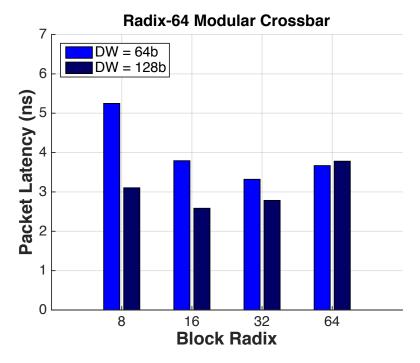

| 4.11 | 32 Byte packet latency for a radix-64 modular crossbar using different block      |            |

|      | radices and datawidths.                                                           | 71         |

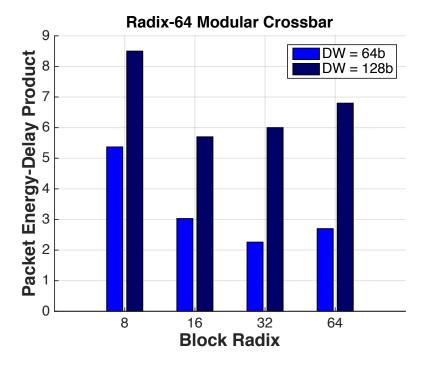

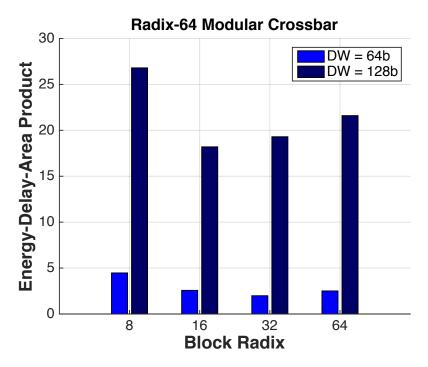

| 4.12 | 32 Byte packet energy-delay product for a radix-64 modular crossbar using         |            |

|      | different block radices and datawidths                                            | 71         |

| 4.13 | 32 Byte packet energy-delay-area product for a radix-64 modular crossbar          |            |

|      | using different block radices and datawidths.                                     | 72         |

| 4.14 | Latency comparison for modular and conventional crossbars with radix scaling.     | 73         |

| 4.15 | Energy comparison for modular and conventional crossbars with radix scaling.      | 73         |

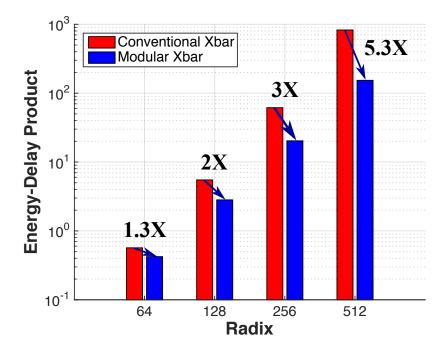

| 4.16 | Energy-delay product comparisons for modular and conventional crossbars           |            |

|      | with radix scaling.                                                               | 74         |

| 4.17 | Area comparison for modular and conventional crossbars for different radices.           | 75 |

|------|-----------------------------------------------------------------------------------------|----|

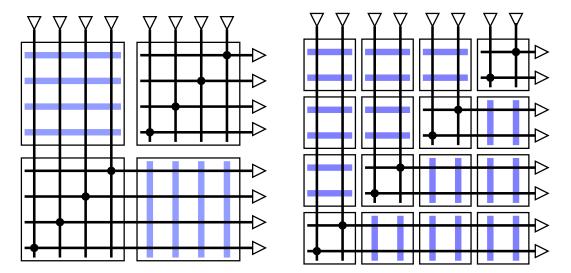

| 5.1  | Top level layout of test chip                                                           | 78 |

| 5.2  | Top level block diagram of the test chip                                                | 79 |

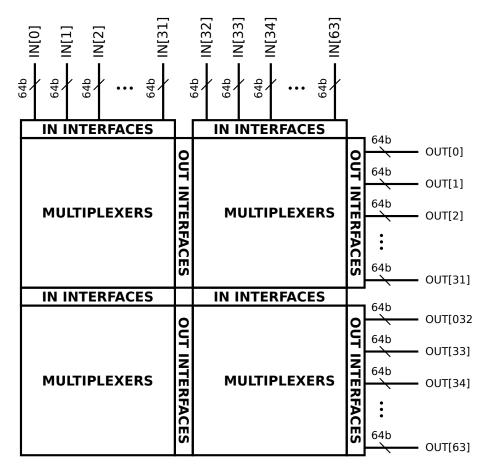

| 5.3  | Radix-64 64bits modular crossbar switch built using radix-32 blocks                     | 80 |

| 5.4  | Floorplan of the radix-64 modular crossbar switch.                                      | 81 |

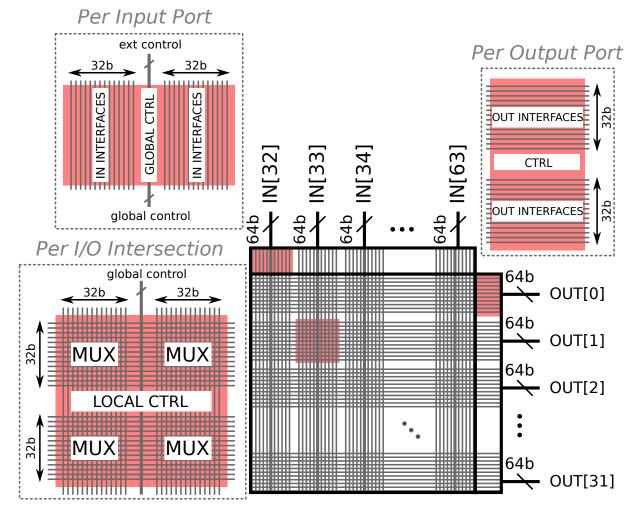

| 5.5  | Floorplan of the radix-32 switch block                                                  | 82 |

| 5.6  | Radix-32 1bit crossbar switch block with input interfaces, multiplexers, out-           |    |

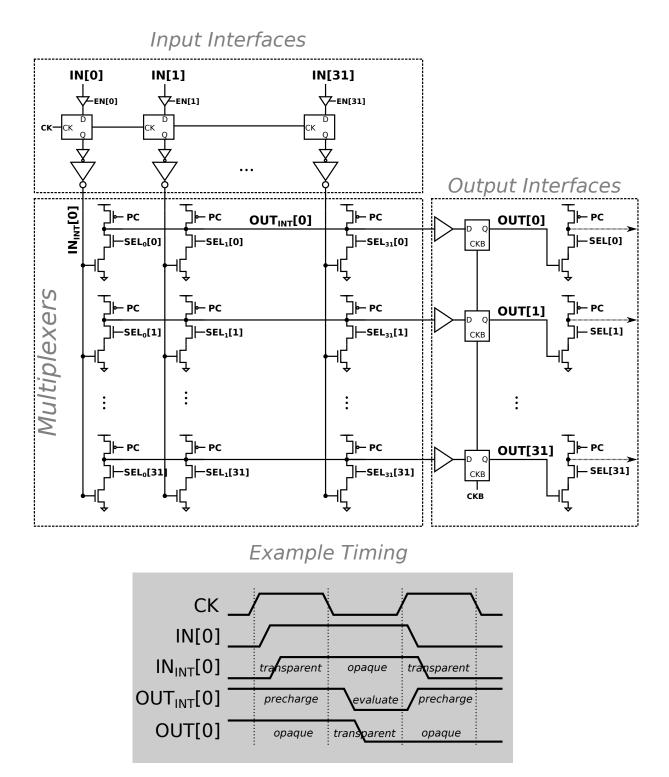

|      | put interfaces, and an example timing diagram                                           | 84 |

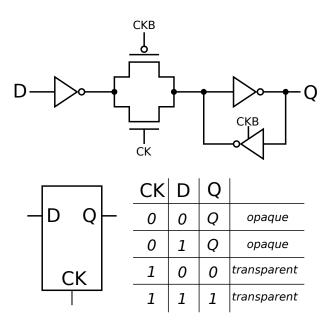

| 5.7  | Active-High D-latch.                                                                    | 86 |

| 5.8  | Layout of a tri-state buffer connecting a single input and output data                  | 87 |

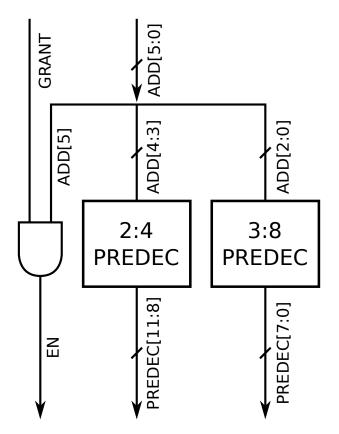

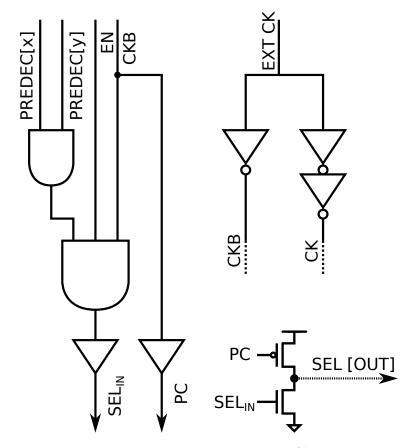

| 5.9  | Global control circuits per input port                                                  | 89 |

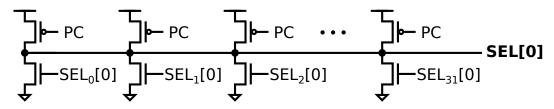

| 5.10 | Local control circuits per I/O port                                                     | 91 |

| 5.11 | Select signal generation for data propagation                                           | 92 |

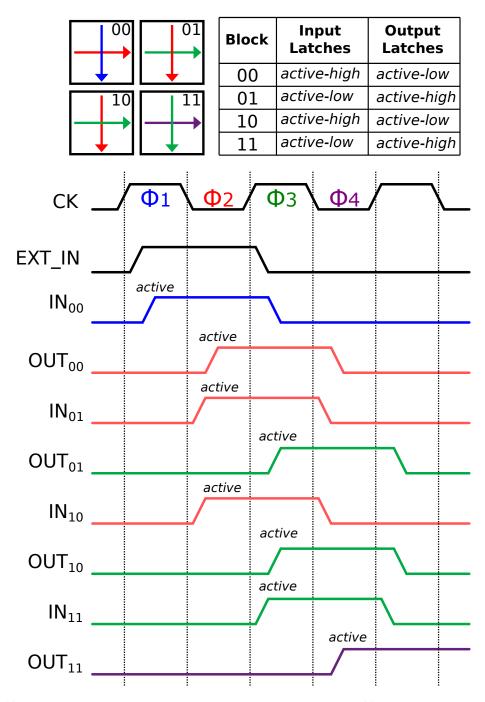

| 5.12 | Clocking scheme for a modular crossbar with 4 blocks. Block 00 inputs are               |    |

|      | distributed in $\Phi 1$ , and Block 00 outputs are generated in $\Phi 2$ . Block 01 and |    |

|      | Block 10 inputs are distributed in $\Phi 2$ , and Block 01 and Block 10 outputs         |    |

|      | are generated or propogated in $\Phi 3$ . Block 11 inputs are distributed in $\Phi 3$ , |    |

|      | and Block 11 outputs are generated or propogated in $\Phi 4. \dots \dots \dots$         | 94 |

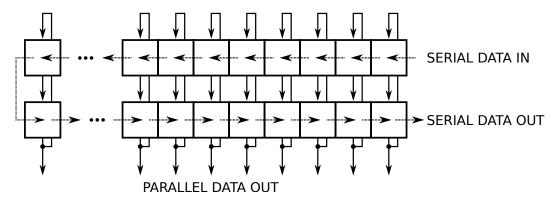

| 5.13 | 2 banks of shift registers built using scan flip-flops. Test I/O of the flip flops      |    |

|      | are connected in series for scan mode, and D and Q of the flip-flops are                |    |

|      | connected in parallel with the next bank for core operation mode. $\ldots$ .            | 95 |

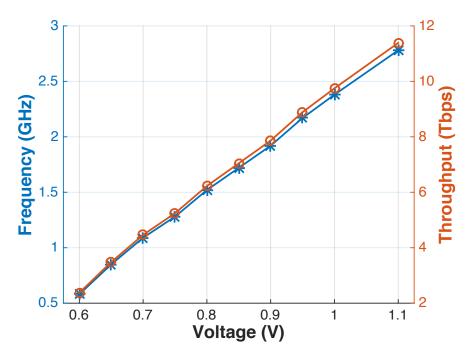

| 5.14 | Frequency and throughput scaling with supply voltage                                    | 96 |

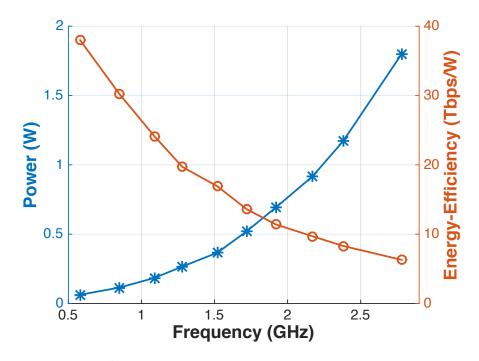

| 5.15 | Power and energy-efficiency scaling with frequency.                                     | 96 |

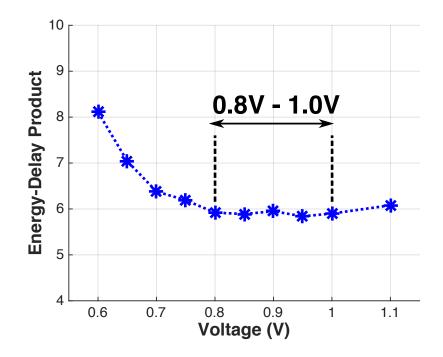

| 5.16 | Energy-delay product scaling with voltage.                                              | 97 |

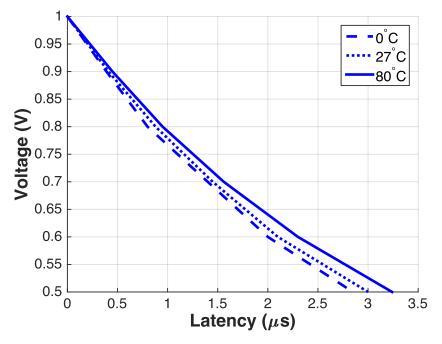

| 5.17 | Voltage droop of floating output nodes.                                                 | 98 |

|      |                                                                                         |    |

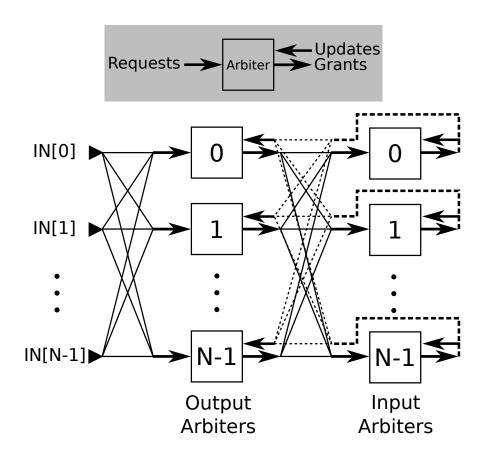

6.1 Modular crossbar architecture with modular flow-through switch, centralized allocator, and combined input and output queueing with virtual channels(VC).103

| 6.2 | Output-first eperable allocation.                                          | 106 |

|-----|----------------------------------------------------------------------------|-----|

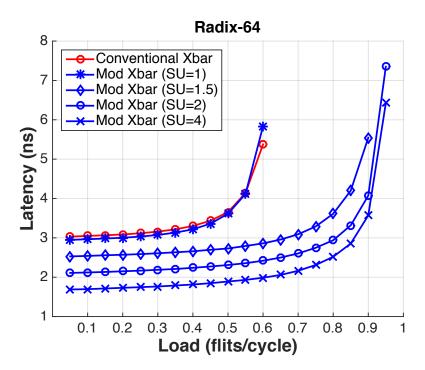

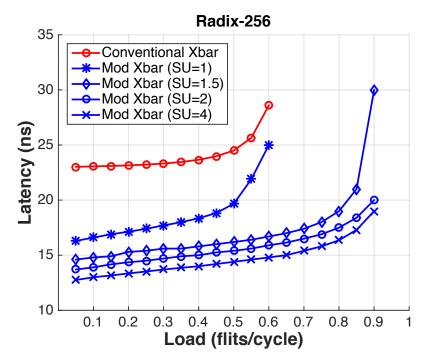

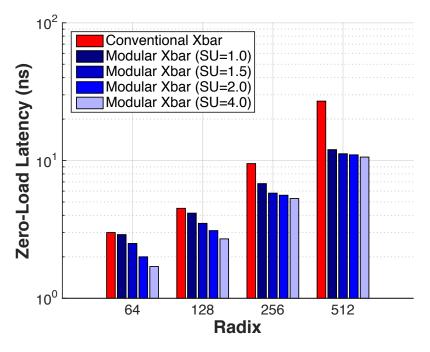

| 6.3 | Load-latency curves for radix-64 conventional and modular crossbars (with  |     |

|     | speedup 1, 1.5, 2, and 4)                                                  | 111 |

| 6.4 | Load-latency curves for radix-128 conventional and modular crossbars (with |     |

|     | speedup 1, 1.5, 2, and 4)                                                  | 112 |

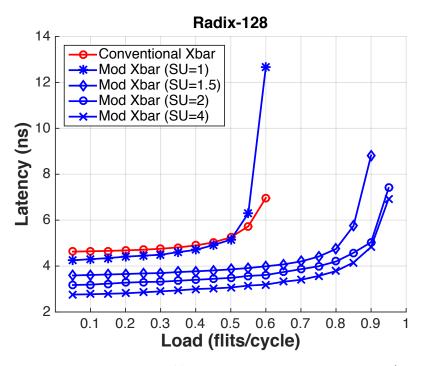

| 6.5 | Load-latency curves for radix-256 conventional and modular crossbars (with |     |

|     | speedup 1, 1.5, 2, and 4)                                                  | 112 |

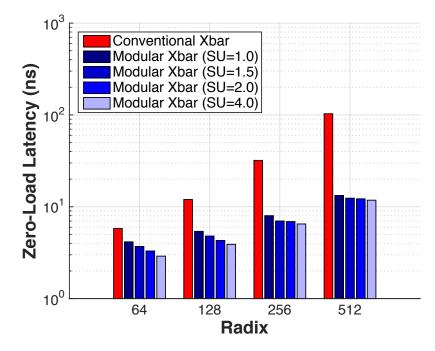

| 6.6 | Zero-load latency for a single-flit packet transfer                        | 114 |

| 6.7 | Zero-load latency for a 32 Byte packet transfer.                           | 114 |

# List of Tables

| 3.1 | Frequency, Power, Area, and Tbps/W Comparison                          | 50  |

|-----|------------------------------------------------------------------------|-----|

| 5.1 | Technology and Testchip Features                                       | 77  |

| 5.2 | Frequency, Throughput (TP), Power, and Energy-Delay Product Comparison |     |

|     | to Previously Published Results                                        | 98  |

| 6.1 | Radix-64 Modular Crossbar                                              | 110 |

| 6.2 | Zero-Load Latency for a Single-Flit Packet                             | 113 |

| 6.3 | Zero-Load Latency for a 32Byte Packet                                  | 113 |

### Chapter 1

## Introduction

### 1.1 Motivation

Advances in process technologies continue to enhance the performance and available number of transistors on a single die with every new generation as predicted by Moore's Law [36, 55]. Historically, chip designers have focused on delivering smaller, faster, and more efficient single core processors aided by higher clock frequencies and sophisticated microarchitectures advancing single-thread performance. However, rising power density with scaling [63] has resulted in diminishing returns for further increasing the clock frequency with the end of Dennard Scaling [17, 18]. Moreover, single-threaded performance reached its limits with increasing overheads from micro-architectural complexities such as extensive pipelining of instruction streams. Thus, these limitations encouraged designers to explore system-on-chips with multiple cores to meet the growing demand for higher throughput and lower power.

Systems-on-chip exploit parallelism from multiple processing and storage units to improve system performance. With every new generation and increasing transistor budgets, the number of cores on a single die increases instead of the size and complexity of a single core, thus, further advancing the compute throughput from process scaling. However, as the

Figure 1.1: Mesh and Crossbar Topologies.

number of components in the system increases, designing the interconnection infrastructure of these systems becomes challenging [10]. In combination with growing wire delay with process scaling, communication has become one of the major factors that determines the system performance and power consumption.

Traditional buses have failed to meet the performance requirements of recent systems-onchip with large number of cores. In spite of its low-cost and simplicity, shared bus connections cannot scale efficiently due to serial utilization. Networks on chip (NoC) emerged as an alternative by offering highly scalable, reliable, and modular communication platforms.

They are constructed from point-to-point data links (channels) and routers [4, 6, 16, 26] that transfer data packets from source to destination ports. Multi-hop networks like mesh (Figure 1.1) are easy to design and scalable to high-radices due to small router sizes and short channels. However, in these networks, data travels through multiple routers, where every router point computes the next-hop route and arbitrates multiple data packets. Hence, they have nonuniform latency and significant programming complexity. In contrast, crossbars are a single-hop, non-blocking network that offer all-to-all communication, with non-uniform latency, programming simplicity, and deterministic fairness [41, 53]. However, it is harder to design due to the large router switch that connects every I/O port.

Although crossbars have been quite popular for system-on-chip designs with low-tomedium

Figure 1.2: Networks-on-Chip in Recent Multi-Core Processors.

number of cores due to their simplicity, recent multi-core processor have replaced crossbars with multi-stage networks such as rings and meshes as seen in Figure 1.2 [3, 7, 47]. Designing high-radix crossbars is a challenge due to the quadratic cost scaling of the router. The crossbar interconnection switch, memory resources, and allocation logic typically scale poorly in area, power, and latency/throughput with increasing radix.

Improving crossbar scalability benefits many communication platforms ranging from systemon-chip and large-scale system networks to high-end Internet routers as the crossbar switch fabric is the main building block. High-radix crossbars can be used as fast, single-stage networks for large system-on-chips. As the use-case for such high-radix crossbars typically involves physically disparate input and output nodes (e.g., multiple processors communicating with multiple L3 cache blocks), these structures are usually built as a compact, centralized crossbar connected to the input and output nodes via dedicated point-to-point data links [41] as seen in Figure 1.3.

High-performance Internet routers and switches also commonly use one-hop high-radix crossbars as the switching fabric that determines the scalability and performance of the Internet. Further, high-radix crossbars can also be used as high-radix routers for largescale networks for larger systems like super computers and datacenters. High-radix routers became critical in building large-scale networks with the emerging high-speed signaling technologies [23, 30] and increased available off-chip bandwidth [14]. Previous work [27] has shown that advancement in available off-chip bandwidth is best exploited by using high-

Figure 1.3: System view of a crossbar network.

radix routers with thin channels, rather than making ports wider. Networks built with high-radix routers reduce the hop count, leads to a lower network latency and cost. Therefore, there is significant effort to improve the scalability, performance, and energy-efficiency of crossbars.

### **1.2 High-Radix Crossbars**

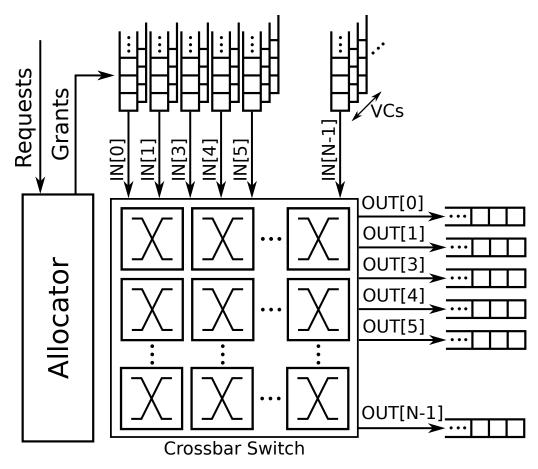

The crossbar network consists of the crossbar switch, I/O buffers, and allocators as seen in 1.4. The switch is the core of the network, offering all-to-all connectivity for I/O ports. The buffers are required to store the incoming and outgoing data in cases of conflicts, and allocators schedule and manage the network resources such as buffer availability and the switch traversal.

The main challenges in designing high-radix crossbars are the complex allocation, increased number of memory resources required, and the physical design of the crossbar switch itself. Previous work has shown that the scheduling of high-radix crossbars is a surmountable challenge [12, 27, 41, 64]. Further, as the network data packet size is usually larger than the physical data width of the crossbar, the scheduling decision latency can be amortized over the multiple cycles required to transfer the entire network packet across the crossbar.

Figure 1.4: Crossbar Architecture.

On the other hand, crossbar switch performance plays a crucial role in high-radix crossbar network performance. Internal switch speedup simplifies allocation and enables high network saturation capacity with low memory cost. Therefore, high-performance switches can enable building efficient high-radix crossbar networks. However, designing a high-radix switch is a challenge. As number of inputs and outputs (radix) of the switch scales, the area grows quadratically (Figure 1.5), hence increasing the latency and energy consumption significantly.

In this thesis, we present a detailed switch design space exploration using a crossbar modeling tool to understand the scaling limitations better. We also discuss circuit and microarchitecture techniques to improve performance and energy-efficiency of high-radix crossbar switches. More specifically, we present a low-swing crossbar switch with high energyefficiency, and a modular crossbar switch that can achieve linear performance scaling. Further, we present a scalable, high-radix modular crossbar that can offer high saturation throughput and low network latency using the high-performance modular switch.

Figure 1.5: Crossbar switch area depends on radix (quadratically) and the I/O intersection width and height.

### 1.3 Dissertation Organization

The crossbar switch architecture is discussed in detail to understand the scaling limitations in Chapter 2. We present a crossbar switch modeling tool for fast design space exploration. We then discuss the trends for various design parameters at system, circuit, and layout level, and present guidelines on how to optimize design parameters for a high-performance, energy-efficient switch.

Chapter 3 explores low-swing signaling to further improve energy-efficiency of crossbar switches. We present a low-swing crossbar switch that uses capacitively coupled I/O wires and multiplexers. We evaluate performance, energy consumption, and area and discuss scaling of the proposed crossbar switch.

Chapter 4 introduces a modular crossbar switch that offers linear performance scaling and energy savings. We build high-performance and energy-efficient switch blocks using the design space exploration results. We then use these blocks to build modular high-radix crossbars that can perform better than monolithic switches. Details of the switch architecture and evaluation are discussed in this chapter.

To validate improvements of our design, we designed and implemented a prototype modular crossbar switch testchip. Chapter 5 describes the testchip in detail and discusses the layout extracted simulation results.

Finally, the modular crossbar network architecture is presented in Chapter 6. The modular architecture consists of the modular switch, centralized allocators, and I/O buffers. The network performance is evaluated using a cycle-accurate NoC evaluation tool. The modular crossbar network offers high saturation throughput and lower network latency with the internal switch speedup.

### Chapter 2

## **Design Space Exploration**

In this chapter, we discuss details of the crossbar switch architecture and define the system, circuit, and layout level design parameters. Crossbar switch characteristics (area, power, performance) depend heavily on the floorplanning and layout, and hence the most accurate evaluation is achieved by post-layout or post-route simulations. This makes design optimization via iteration highly time and resource intensive, especially for full custom ASIC designs. Although standard cell designs have more flexibility to optimize system level parameters such as number of modules and data width, these designs lack low level circuit and routing optimizations due to EDA tool limitations.

To better understand the design space, we have developed an on-chip crossbar modeling tool based on analytical models calibrated using circuit-level simulation results in 40nm CMOS. We present a design space exploration showing how crossbar area, power, and performance vary across input/output node number, data width, wire parameters, and circuit implementation.

We also use the crossbar modeling tool (with added modifications) to explore our low-swing and modular crossbar switch ideas to improve energy-efficiency and throughput respectively in the later chapters. The tool allows fast design exploration for novel switch ideas with different parameter constraints. It also allows evaluating the proposed designs at various radices to understand scalability and limitations.

### 2.1 Related Work

The related work most similar to that present here is from Passas *et al.*[41, 43] who present a cost analysis and modeling of crossbar switch area, delay, and power. Their main focus is the crossbar topology and the performance optimization for high radices across different radices and data width. They use standard cell design flow to build multiplexer tree based crossbars for the analysis and report post-route and simulation based results. Using standard cell design flow gives them flexibility to run an automated flow for post-route simulations, but their experiments are limited to multiplexer tree based designs and limited by electronic design automation (EDA) tool routing options. In contrast, our analytical crossbar model covers both system level (number of modules and data width) and circuit level (multiplexer circuits, wire pitches, etc.) design parameters to achieve design optimization as close to full custom design as possible. We further take into account custom layout optimizations that are not possible in the previous standard cell synthesis based modeling work.

As NoCs are in widespread use, other researchers have developed a number of on-chip network modeling tools for design exploration [4, 39, 40, 60, 65, 66, 67]. These tools contain relatively simple crossbar models, as crossbars are typically at the core of routers used in multi-hop networks. Further, these crossbars are typically of low-radix as they only connect the local network node to the rest of the multi-hop network. The crossbar modeling is part of the router modeling and is based on the basic X-Y crossbar design where the inputs and outputs run perpendicular to each other (usually using minimum sized wires) and connected via tri-state buffers at each intersection point. These studies focus on the modeling and optimization of the entire multi-hop network itself. Although they provide good system level modeling and exploration, the crossbar design options are not explored, the modeling is at a relatively high level, and the radix of the crossbars modeled is relatively low.

Finally, in the circuit design space, researchers have proposed improvement techniques for X-Y topology crossbar switches [11, 45, 51, 52, 53, 54, 58, 69]. However, these are isolated point designs and there has not been significant exploration of the design space at the circuit-level owing to the iteration difficulties mentioned earlier. As such, our work allows for incorporation of new circuit techniques into our overall modeling and optimization framework. Indeed, the impetus for our modeling effort was our interest in designing high radix crossbar implementations, and our realization that there was not a modeling/optimization framework with sufficient level of detail and design options.

### 2.2 Crossbar Architecture

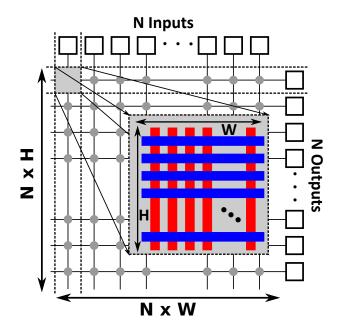

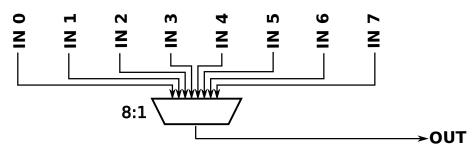

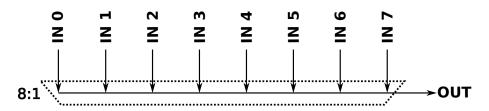

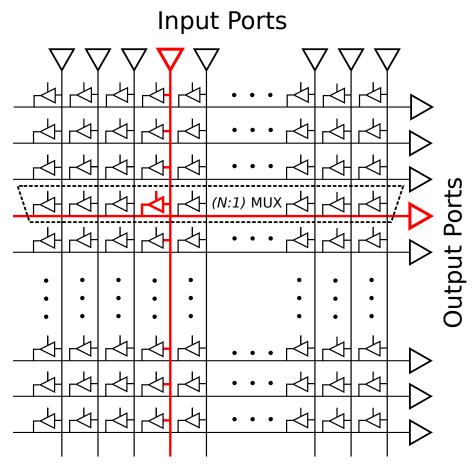

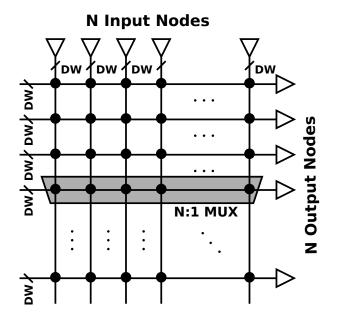

An  $N \ge N$  crossbar is a non-blocking switch that connects N input nodes to N output nodes, where each node has a data width (DW). The crossbar architecture is shown in Figure 2.1, where the connection of every input data to an output forms an N:1 multiplexer.

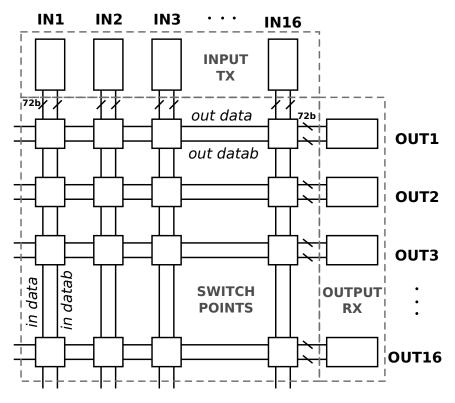

Figure 2.1:  $N \times N$  crossbar architecture, where the connection of every input data to an output forms an N:1 multiplexer.

The crossbar consists of  $N \ge DW$  input data bits,  $N \ge DW$  output data bits, and  $N \ge DW$  multiplexers, N:1 each. As N and DW increases, floorplanning and the total design area become significant parts of the performance due to large number of long I/O wires, multiplexers, and challenging routing requirements. Physical design details such as floorplanning and area, as well as circuit details of multiplexers and I/O wires are discussed below.

### 2.2.1 Floorplanning

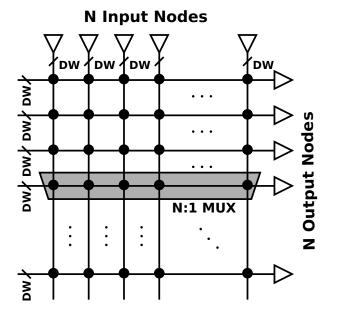

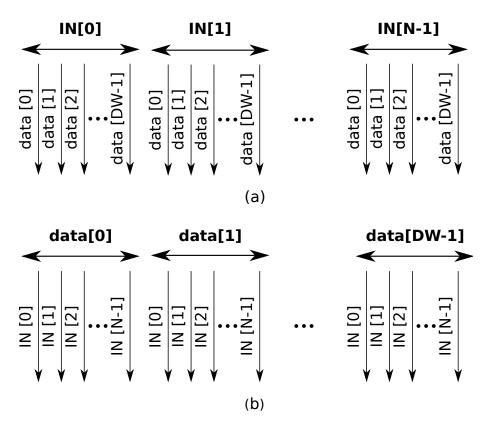

One challenge in crossbar design is to arrange I/O data wires for easier access to/from multiplexer gates from/to edge of the design. Floorplanning options are port-slicing and bit-slicing as can be seen in Figure 2.2. Grouping the data bits together for each module (port) is called port-slicing. The modules (module [0], module[1],...,module[N]) are placed next to each other where each module has DW data bits. This requires the output multiplexers to span the whole design width to get inputs from each module. On the other hand, grouping together a specific data from each module is called bit-slicing. In this case, data bits (data[0], data[1],...,data[DW]) are placed next to each other where each group has N data bits (one data bit from each module). This enables building smaller and faster multiplexers as inputs of each multiplexer are already grouped.

However, it is typical to assume that the I/O data bits are grouped together for each node and routed to/from the edge of the crossbar design. Therefore, for bit-slicing, a rearrangement of the I/O data bits at the edge of the design is required. For large number of I/O data bits, this bit scrambling requires a large area, and extra clock cycles [41]. Therefore, port-slicing offers better performance overall.

#### 2.2.2 Area

Large number of wires, multiplexers, and the floorplanning details determine the area of the design, which is critical for the electrical parameters of the long I/O wires. Matrix-

Figure 2.2:  $N \times N$  crossbar with DW data bits implemented using port-slicing (a) and bit-slicing (b) floorplans.

style wiring, where input and output wires run perpendicular to each other, maximizes area utilization. Optimum size multiplexers usually fit underneath the minimum pitch I/O wires for smaller radix designs, whereas for high radices, using larger wire pitches can improve the performance by increasing the design area for the multiplexers (for better drive strength).

### 2.2.3 Input Wires

Each input bit should be distributed to every output multiplexer that means the input wires should span the whole height of the crossbar. In addition to quadratic latency growth of long input wires, fan out of the input bits increase as the design radix increases. Every multiplexer behaves as a constant load on input wires. Input drivers have more design flexibility as they can be stacked physically without a significant contribution to the overall core area and repeaters can be inserted when needed. However, the input wire delay is still a substantial portion of the overall delay at high radices.

### 2.2.4 Multiplexers and Output Wires

Switch circuits are multiplexers that drive the long output wires. Since we adopted port slicing, each multiplexer spans the whole design width to access all input nodes and drives long output wires. Internal wires of the multiplexers are not negligible, and this increases the delay by adding intrinsic wire delay and extra load capacitance from the wires. Further, as they are placed underneath the I/O wires to have a smaller crossbar area, the multiplexer area, hence the drive strength, is limited.

#### Architectural Implementation Options

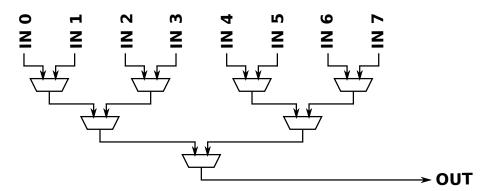

Designing a N:1 multiplexer, where N is large, is a challenge due to parasitic loading from the non-active inputs. A popular solution is to build the large radix multiplexer using smaller radix sub-multiplexers in a tree-structure to improve the performance. In a flat multiplexer implementation, a single horizontal wire track is dedicated for every output bit. But if the multiplexer is built as a tree, the number of horizontal wire tracks is increased to  $\log_{m} N$  (the depth of the tree where *m* is sub-multiplexer radix) as seen in Figure 2.3. The length of the internal wires between the sub-multiplexers depend on the physical implementation choices as will be explained below. Further, increasing the depth of the multiplexer increases the design area, hence effecting the length and latency performance of I/O wires.

Figure 2.3: 8:1 multiplexer built using 2:1 sub-multiplexers.

#### **Physical Implementation Options**

As the inputs of the multiplexers span a large area, there are two main physical multiplexer implementation options: the distributed and centralized styles. The centralized style routes all the inputs to the multiplexer located in the middle and drives the output wire from that location, whereas in the distributed approach, the output wire spans all the input locations and the inputs tap-on to the output. Figure 2.4 and 2.5 show the centralized and distributed style implementations of an 8:1 multiplexer respectively. The centralized style minimizes the internal wires of the multiplexer, but it requires more horizontal wires dedicated to the input routing of multiplexers and suffers from larger area at higher radices. On the other hand, the distributed style has longer internal wires and cannot use unidirectional repeaters on the internal and output wires and suffers from quadratic wire delay scaling.

Figure 2.4: (a) Centralized physical implementation of a 8:1 multiplexer.

Figure 2.5: (b) Distributed physical implementation of a 8:1 multiplexer.

### **Circuit Implementation Options**

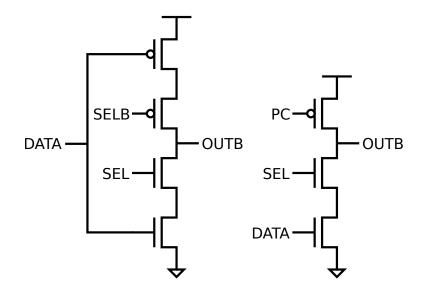

The critical path of the crossbar is the data propagation through the longest input wire to the longest output wire, which means the switch circuit connects two high resistive paths and has high susceptibility to noise. Therefore static tri-state inverters are used to implement the multiplexers as they offer good performance due to low resistive paths to ground/power. The crossbar multiplexer is built by wiring together the tri-state inverters for each input module (different options of architecture and physical implementation are discussed above). Every input module has a select signal that is activated if the input is granted priority. Therefore, only the chosen input module's tri-state inverter drives the output wire.

We also explored using dynamic tri-state buffers for crossbar multiplexers. For hierarchical multiplexer implementations, precharging internal wires (sub-multiplexer outputs) are not feasible due to high switching energy, and extra wire routing for the precharge signal for each stage. But, it is an appealing option for flat multiplexer implementations since only the output wire is precharged and it avoids the large PMOS pull-up devices. The PMOS transistor used for the precharge can be sized smaller, since the unselected tri-state inverters

shares the same precharge signal and will also pull-up the output wires.

Figure 2.6 shows a static tri-state inverter (left) and a dynamic tri-state inverter. The static tri-state inverter drives the output wires when the input module is granted priority (SEL = 1). The dynamic tri-state inverter output is initially precharged high (PC = 0), and when in operating mode (PC = 1), the output is pulled-down if the input module is granted priority and the data is high.

Figure 2.6: A static (left) and a dynamic (right) tri-state inverters.

## 2.3 Crossbar Modeling

We built an analytical model of the crossbar using design options explained in Section 2.2 as design parameters in Matlab. Models for the evaluation metrics (area, delay/throughput, and energy consumption) are calibrated using circuit-level, post-layout simulation results in 40nm CMOS bulk process (tt corner). Using the modeling framework, we present guidelines on how to optimize each parameter for minimum energy-delay product.

### 2.3.1 Design Parameters

The design parameters are listed below.

Number of I/O nodes (N): Radix of the crossbar.

**Data width** (DW): Number of data bits for each I/O node.

- Input and output wire pitches: Sum of the wire width and spacing. Input and output wire pitches are independent from each other and should be optimized considering their electrical wire parameters as well as how they contribute to the total design area.

- Number of metal layers: Number of metal layers dedicated for both input and output wires.

- Sub-multiplexer Radix (m): Radix of the sub-multiplexers that are used to build the N:1 switch multiplexer.

- Multiplexer physical implementation: Options are the centralized or the distributed styles as described above.

### 2.3.2 Evaluation Metrics

Evaluation metrics are area, delay/throughput, and energy consumption. Area is calculated using design parameters. Delay and energy consumption is modeled with design parameters as well as wire characteristics determined by the area and the floorplan.

#### Area

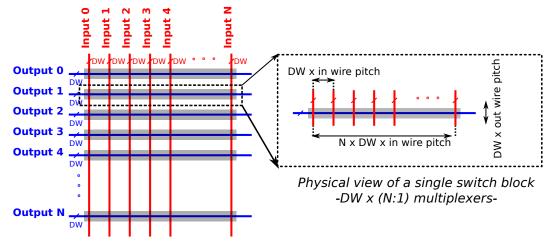

Floorplan of the crossbar design using port-slicing and matrix-style wiring can be seen in Figure 2.7. The area is dominated by the I/O wires and the switch circuits can be placed

underneath the wires. Details of a single switch block for an output port is shown as well.

Figure 2.7: Floorplan of an NxN crossbar.

I/O wire length and design area are calculated as in Equation 2.1 and 2.2. Area is calculated using radix, datawidth, I/O wire pitches, and number of metal layers. Increasing the I/O wire width would decrease the wire resistance, however would increase the wire capacitance and design area. Input wire pitch determines the output wire length and vice versa. Therefore, it is important to understand the trade-offs for crossbar wire engineering, as the matrix style wire structure in the crossbar creates an interdependence of wire pitches and wire lengths. Further, area can be decreased by using more metal layers. However, smaller area also limits the size of switch circuits, hence limits the drive strength.

$$wire length_{i/o} = \frac{wire \, pitch_{o/i} \times DW \times N}{number \, of \, metal \, layers} \tag{2.1}$$

$$area = wire \, length_i \times wire \, length_o \tag{2.2}$$

### **Delay and Throughput**

I/O wires play a substantial role in both delay and energy consumption. Wires are modeled as distributed RC lines [21]. Wire capacitance ( $C_{wire}$ , sum of four parallel-plate capacitances plus a fringe capacitance) and wire resistance ( $R_{wire}$ ) are calculated using wire length, width, and spacing.

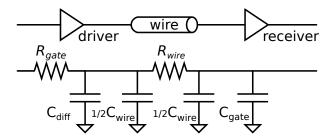

Figure 2.8: RC modeling of the driver, wire, and receiver for delay calculations.

Delay is modeled by RC formulation as seen in Equation 2.3. Drivers are modeled as resistors ( $R_{gate}$ ) with parasitic loads ( $C_{diff}$ ), and receivers present capacitive loads ( $C_{gate}$ ). Delay for Figure 2.8 is calculated as in Equation 2.3.

$$\tau = R_{gate} \times (C_{diff} + C_{wire}) + R_{wire} \times (1/2C_{wire} + C_{gate})$$

$$(2.3)$$

*Input Wire Delay*: Input data is distributed to every output multiplexer which behaves as a constant receiver load. Since receivers are distributed throughout the wire, parasitic loads contribute to the delay similarly as the distributed wire capacitance.

$$\tau_{input} = R_{gate} \times (C_{diff} + C_{wire} + N_o C_{gate}) + R_{wire} \times (1/2C_{wire} + 1/2N_o C_{gate}) \quad (2.4)$$

Multiplexer and Output Wire Delay: The multiplexers drive the long output wires and the delay is modeled for different physical implementation styles as shown below. If built in a tree-structure, each sub-multiplexer drives a wire since the internal wires are not negligible

and the final sub-multiplexer drives the output wire. The delay is the sum of all submultiplexer delays as in Equation 2.5 and 2.6.

For the centralized style, switch drivers (tri-state buffers) of the multiplexer are the wire drivers, and the driver parasitic load is not only the  $C_{\text{diff}}$  of the driver gate, but also the sum of all the unselected switch driver parasitic loads. If the input of the multiplexer (m) is larger than 4 (can be anything from 2 to N), we build it as quad-tree multiplexer using 4:1 multiplexers, since it is the most optimal way [61], and calculate the overall delay as the sum of the delay of each stage (as in Equation 2.5).

$$\tau_{centralized} = R_{gate} \times (mC_{diff} + C_{wire} + C_{gate}) + R_{wire} \times (1/2C_{wire} + C_{gate}) \quad (2.5)$$

For the distributed style, switch drivers of the multiplexer are distributed throughout the output wire; therefore the parasitic load from the unselected drivers can be modeled as extra distributed parasitic loading on the selected driver as well as the wire resistance.

$$\tau_{distributed} = R_{gate} \times (mC_{diff} + C_{wire} + C_{gate}) + R_{wire} \times (1/2C_{wire} + 1/2mC_{diff} + C_{gate}) \quad (2.6)$$

Size of the network packet is usually larger than the DW. In order find the optimum DW, the throughput (TP) of the design is also evaluated.

$$TP = DW \times \frac{1}{delay} \tag{2.7}$$

### Energy

Our energy modeling focuses on the switch capacitive current and energy consumption is modeled as in Equation 2.8 where  $C_{wire}$  is the sum of input, output and internal switching wire capacitances and  $C_{mux}$  is the sum of the gate and diffusion capacitances of the switching devices of the multiplexers for a single data bit.

$$energy = N \times DW \times (C_{wire}VDD^2 + C_{mux}VDD^2)$$

(2.8)

### 2.3.3 Methodology

For a given N, we calculate area, delay, and energy using the models explained above in a flow shown below. In order to find the optimum design point, the flow is repeated for every possible set of design parameters.

- 1. Input N

- 2. Set the design parameters : *DW*, number of metal layers, input and output wire pitch, sub-multiplexer radix, multiplexer physical implementation style

- 3. Calculate I/O wire lengths and design area

- 4. Placement of multiplexers: Multiplexer tree is structured and each sub-multiplexer is placed.

- 5. Calculate wire parasitics for I/O wires and the internal wires for the multiplexers: Length of the internal wires are calculated from locations of the current and the next sub-multiplexers.

- 6. Size the multiplexers:

- If built as a tree, sizing starts from the last sub-multiplexer.

- Multiplexer is sized according to optimal fan out (FO) sizing [61] where load is gate capacitance of the next multiplexer and the wire capacitances.

- Each multiplexer in the tree has an allowed area that is decided by design area and number of multiplexers in the tree.

- If the sized multiplexer does not fit in that area, *FO* is increased until the multiplexer is small enough.

- 7. Calculate delay and energy for multiplexers and output wires: Sum of delay and energy of all multiplexer stages.

- 8. Calculate delay and energy for input wires: Repeaters are inserted if necessary.

- 9. Calculate the total delay and energy

## 2.4 Evaluation

We run this flow for different sets of design parameters to understand the behavior of each parameter and the optimal design points. While sweeping a specific parameter, the rest of the parameters are set to the most optimal solution for that specific design point. First, we explore sub-multiplexer radix and the physical implementation style that lead us to an optimum design option. Using this design point, we look into the trends for the wire pitch and the number of metal layers. Further, we examine the effects of DW on performance and changes with radix scaling. Finally, we highlight a design point optimized for minimum energy-delay product and compared its performance to previously published results.

### 2.4.1 Sub-multiplexer Radix

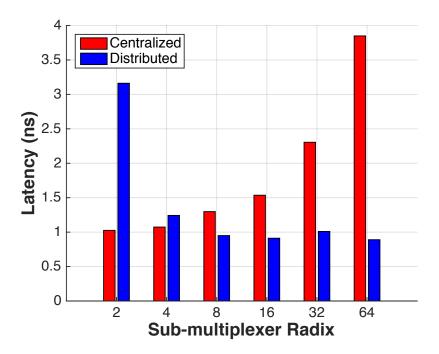

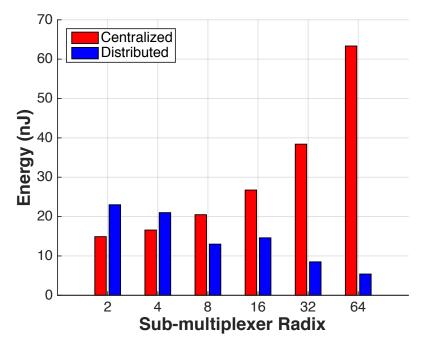

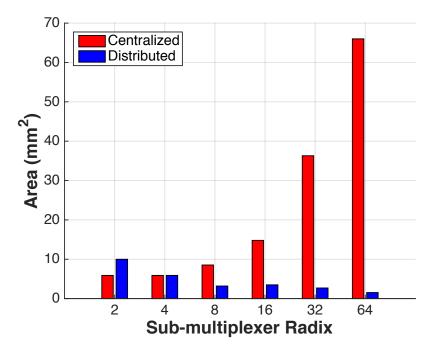

The sub-multiplexer radix (m) is swept from 2 (binary tree) to N (flat) for both the centralized and distributed implementation styles to find the optimum design point. Figure 2.9, 2.10, and 2.11 show comparisons of delay, energy, and area of centralized and distributed styles with different sub-multiplexer radices.

For the centralized style, the most optimal implementation is to use a binary-tree multiplexer (m=2). The multiplexer is located in the middle where all the distributed inputs are driven to, therefore every stage of multiplexers have m/2 extra horizontal wire tracks dedicated for input wires. This results in a larger area, higher energy consumption, and delay with increasing m.

On the other hand, for the distributed style, the best performance can be achieved using a flat multiplexer (m = N). This implementation does not have extra wire tracks for the inputs that limits the m, and since the distributed inputs are connected via long wires, the parasitic loading from the other inputs are negligible.

Figure 2.9: Latency of centralized and distributed styles with different sub-multiplexer radices.

Figure 2.10: Energy of centralized and distributed styles with different sub-multiplexer radices.

Figure 2.11: Area of centralized and distributed styles with different sub-multiplexer radices.

### 2.4.2 Physical Implementation Style

We compared the performance of different physical implementation styles. The centralized style is implemented using a binary tree multiplexer, whereas the distributed style is implemented using a flat distributed multiplexer.

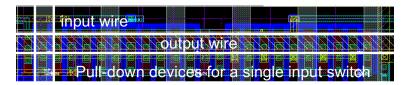

For the distributed, flat multiplexer, there is a single output wire that all inputs are connected to. As mentioned in the previous section, this makes it possible to use dynamic logic to build the multiplexer. The switch connections of the inputs are built as pull down circuits, and pre-charge pull up devices are distributed on the output wire (number of pull up devices depend on the wire capacitance as well as the timing requirements). This style decreases the circuit area significantly by removing large PMOS devices in the tri-state buffers, however introduces additional timing requirements because of the pre-charge scheme.

Figure 2.12, 2.13, 2.14 show comparison of delay, energy, and area of centralized, distributed, and distributed-dynamic styles for a radix-64 crossbar with 64b of data. As can be seen the distributed-dynamic style offers the best performance in terms of delay, energy, and area.

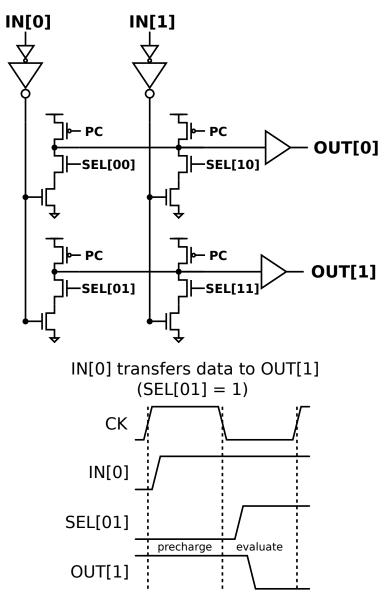

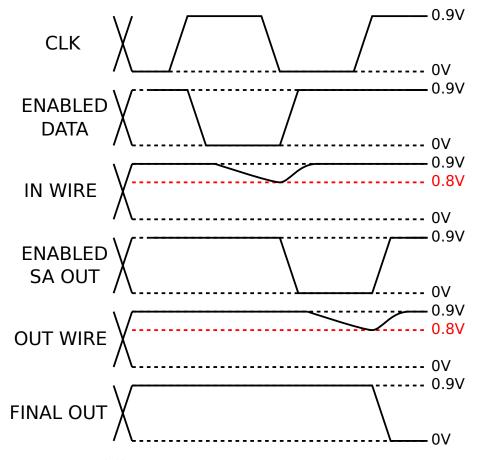

Figure 2.15 shows and example of an 2x2 1b crossbar with distributed-dynamic tri-state buffers. Figure 2.16 shows the circuit details and timing of the 2x2 crossbar. Inputs are distributed on the high-phase of the clock while outputs are precharged and the outputs are evaluated on the low-phase of the clock.

### 2.4.3 Wire Pitch

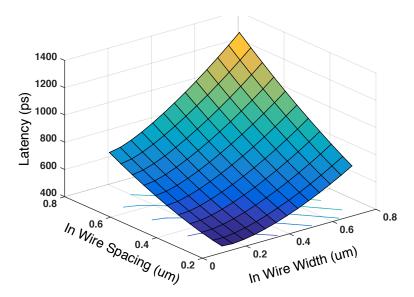

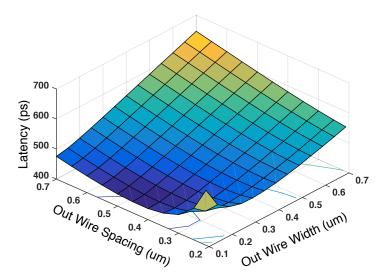

Increasing the input and out wire pitches increases the area as well as the energy consumption. Increasing the design area improves the switch driver strength, hence performance, but also increases the wire capacitance that potentially hurts the performance. The delay for different input and output wire width and spacing can be seen in Figures 2.17 and 2.18. Both the input and output performances are more sensitive to wire width because increas-

Figure 2.12: Latency comparison of of centralized, distributed, and distributed-dynamic styles.

Figure 2.13: Energy comparison of of centralized, distributed, and distributed-dynamic styles.

Figure 2.14: Area comparison of of centralized, distributed, and distributed-dynamic styles.

Figure 2.15: 2 x 2 1b crossbar architecture with distributed-dynamic multiplexers.

Figure 2.16: 2 x 2 1b crossbar circuits.

Figure 2.17: Delay for different input wire width and spacing.

ing the wire width decreases resistance of that wire, improves the switch driver strength, but increases the capacitance of the corresponding wire as well as the opposite wire. On the other hand, increasing the spacing improves the driver strength, and only increases the opposite wire capacitance.

The optimum input wire width and spacing are the minimum values. The optimum output wire spacing is the minimum as well, however the optimum output wire spacing is  $\sim 6$  times more than the minimum spacing. Increasing the output wire spacing increases the output driver area while increasing the input wire capacitance. But since the input drivers have more flexibility in terms of area and drive strength, the overall delay performance is improved with increasing output spacing.

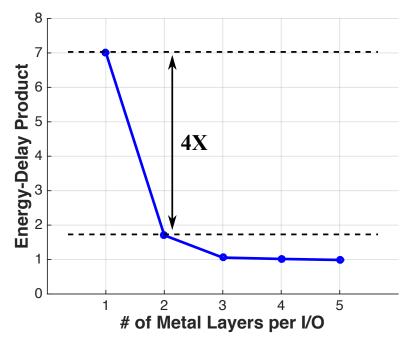

### 2.4.4 Number of Metal Layers

Increasing the number of metal layers dedicated for input and output wires decreases design area linearly. But it also decreases switch driver area; therefore performance improvement saturates when drive strength of the switch circuits degrades significantly and it becomes physically impossible to fit minimum size transistors. Figure 2.19 shows energy-delay prod-

Figure 2.18: Delay for different output wire width and spacing.

uct for different number of metal layers for a radix-64 crossbar with 64bits of data. Using 2 metal layers for each input and output wires (4 layers total) improves energy-delay product ~ 4X. Although using more metal layers improve performance further (at a lower rate), it requires more than 6 layers dedicated just for the high level routing of the crossbar, which is a big portion of wire resources for current technologies.

### 2.4.5 Data Width

Area and energy grows exponentially with data width (DW) scaling. Delay, on the other hand, grows at different rates for different DW values for crossbars.

Increasing the DW increases switch circuit area (improves drive strength) and IO wire lengths. When DW is small, constant overhead delay (timing margins for flip-flops and dynamic logic) and output parasitic loading of the switch is a bigger portion of the delay. Therefore, delay increases at an even lower rate than DW scaling. As DW gets larger, this rate becomes linear, and quadratic when unrepeated wire delay dominates.

throughput (TP) would stay constant with DW scaling if delay would scale linearly. Opti-

Figure 2.19: Energy-delay product vs number of metal layers.

mum design point is where delay starts scaling worse than linear. As shown in Figure 2.20 TP increases until the optimum point and declines afterwards. Furthermore, optimum DW point changes with radix scaling as well. Optimum DW is larger for smaller radices and vice versa as seen in Figure 2.20 as the main bottleneck of the crossbar design is total area determined by N and DW.

## 2.5 Summary

In this chapter, we present a modeling tool for crossbar design to have a better understanding of the design space and parameters. Our design space exploration suggests that smaller designs offer better performance due to shorter input, output and internal wires. Both input and output wire widths should be minimized to decrease the design area and wire capacitances. Wire spacing, on the other hand, can be increased to improve the multiplexer drive strength. Smallest switch option that offers the best performance is flat multiplexers

Figure 2.20: Throughput for different data widths and radices.

built with domino-style tri-state buffers. The optimum data width of the design depends on the radix and should be chosen to keep design area reasonable. Next chapter will explore low-swing signaling to improve energy-efficiency of crossbar switches and present a low-swing crossbar switch design using capacitive coupling.

## Chapter 3

# Low Power Crossbar Circuits

In this chapter, we explore low-swing signaling to improve energy-efficiency of crossbar switches. Switching energy of long I/O wires are one of the major contributors to the high energy consumption of crossbar switches. [58] presents an energy efficient crossbar that uses low-swing signaling by using early detection as in SRAM bit lines, and [29, 45] demonstrates another crossbar with reduced voltage swings using dual voltage supply, differential, reduced-swing drivers. We propose a low-swing crossbar design that uses capacitively driven wires [22, 56] and capacitively coupled multiplexers [8]. The long input wires are driven with series coupling capacitances that pre-emphasize transitions to reduce wire delay and to reduce the load seen by the driver. It also lowers the voltage swing without the need of a second voltage supply, thus, offering low swing signaling, higher bandwidth, and low energy. A capacitively coupled multiplexer uses a similar drive scheme for the inputs to drive a common node. A particular advantage of this scheme is that the un-selected inputs present a lower parasitic loading because the coupling MOS capacitors used to drive the wire are off, and thus have a lowered capacitance.

### 3.1 Low-Swing Crossbar Switch Design

Our low-swing crossbar switch design adapts matrix-style wiring where input and output wires run perpendicular to each other (inputs run vertically whereas outputs run horizontally) to minimize the design area. Further, as common practice, the I/O data for each module is routed to/from the edges of the crossbar design. Thus, I/O data for each module is also grouped within the design (also called port-slicing) in order to avoid extra I/O scrambling at the edges. However, this means that input wires span the entire height of the design to distribute the data to every multiplexer, and multiplexers span the entire width of the design. Distributed inputs of the multiplexers (from each input module) are connected to the output wires via switches to form the multiplexers.

Even for minimum pitch wires and low-radix crossbar designs, the wire parasitics are significant. The quadratic wire latency increase can be mitigated by repeater insertion, but repeaters come at an energy and area cost. In order to improve both latency and energy consumption, we propose to use capacitively coupled wires [22, 56]. Another major bottleneck for crossbars is the needed multiplexer structures. Designing an N:1 multiplexer, where N is large, is a challenge due to parasitic loading from the unselected inputs. Further, the multiplexers are required to drive the long output wires. Capacitively coupled multiplexers can improve the performance of high-radix multiplexers where the un-selected input capacitances are significantly smaller than the active input capacitance and driving the output wires capacitively. The idea and the implementation as the crossbar switch are also explained in detail in this section.

### 3.1.1 Capacitively Coupled Wires

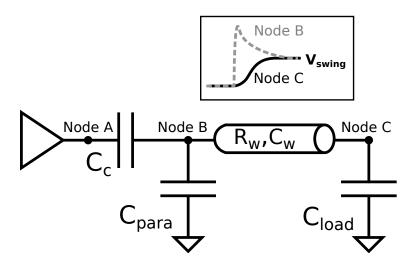

Driving a long wire through a series coupling capacitor as seen in Fig. 3.1 reduces the signal swing through a capacitive voltage divider [22, 35, 49, 56]. While a conventional driver drives the coupling capacitance with a full-swing voltage transition (at node A), the

Figure 3.1: A capacitively driven wire scheme.

very end of the wire (node C) only receives a reduced voltage transition due to the capacitive divider formed by the coupling capacitance, the wire capacitance, and the load and parasitic capacitances as can be seen in Equation 3.1. Node B will initially overshoot and then settle to  $V_{swing}$ , while node C shows a rapid rise to  $V_{swing}$ . The coupling capacitance can be sized depending on the desired voltage swing on the wires.

$$V_{swing} = V_{dd} \frac{C_c}{C_c + C_w + C_{para} + C_{load}}$$

(3.1)

One of benefits of this scheme is the latency improvement through pre-emphasis and the reduced energy consumption. This is faster than an inverter driving a wire because the driver sees only  $C_c$  not the  $C_{wire}$ , and the charge redistribution across the wire cuts the wire delay approximately in half as seen in Equation 3.2. For our implementation, we sized the coupling capacitance for twice the desired reduced voltage swing and sense when the voltage drop reaches the desired voltage swing.

$$\tau \approx R_{driver}(C_c + C_{driver, para}) + R_w C_w / 4w \tag{3.2}$$

Further, the wire switching energy improves linearly with the reduced voltage swing without requiring a second voltage supply as seen in Equation 3.3, and the overall energy consump-

tion also improves significantly with the reduced size of the drivers since it only sees the  $C_c$ . The required differential wiring and the sense amplifiers to restore the low-swing signals reduces the total energy savings marginally. For example, a 10mm long capacitively driven wire with 1/9th of Vdd swing offers 3.8X better energy savings compared to long full-swing buses optimized for lowest energy-delay product in 180nm CMOS bulk process [22].

$$Energy_{wire} = C_{wire}V_{swing}Vdd \tag{3.3}$$

We designed capacitively coupled input data transmitters and input receivers for the lowswing crossbar design.

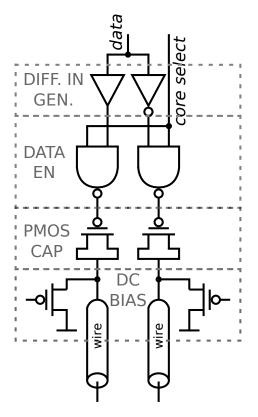

### 3.1.2 Capacitively Coupled Input Data Transmitters

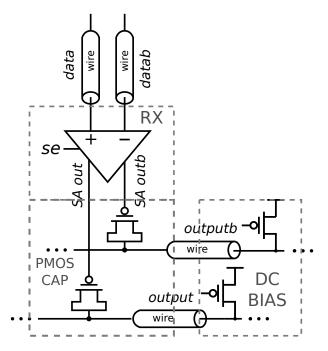

Capacitively coupled input data transmitters are designed to drive the long input wires and the detailed circuit is shown in Fig. 3.2. The transmitter consists of differential input generator, NAND gates for data enable and energy reduction, drain-source connected PMOS gates as the series coupling capacitances, and the PMOS gates as the precharge devices for DC biasing.

The reduced voltage swing comes with reduced noise margins. In order to reduce the crosstalk from the neighbors and the complementary data signals, twisted and interleaved differential wires are used to distribute the data [22, 46]. The overhead of using twice the wire resources for the differential wiring is reflected in the total design area.

Drain source connected PMOS transistor acts like a nonlinear capacitance. The gateto-source and gate-to-drain capacitances of the PMOS are higher when the transistor is enhancement mode due to the channel formed underneath the gate. Therefore, the drain source connected PMOS has a high capacitance when the device is turned-on. The output port of the PMOS capacitance is biased high at Vdd. If the data is not enabled, the output of the NAND gate is also high, hence no transition on the input data wires. But when the

Figure 3.2: Capacitively coupled input data transmitters.

data is enabled, the high-to-low transition on the NAND output propagates through the input wires via the on PMOS capacitance. The size of the capacitance can be adjusted by changing the width and length of the transistor.

The data wires need a path to a DC source to have the proper DC bias. We adopted a precharge scheme where the input and output data wires operate on different phases of the clock and precharged when not in use. The precharge transistors are distributed throughout the wire and sized accordingly to meet the timing requirements.

### 3.1.3 Input Data Receivers

Data for every input module is received by the output multiplexers. The receivers present a parasitic load capacitance on the input wires (total load scales linearly with N), and this is also included in the latency and energy calculations and the corresponding input transmitter sizing. StrongARM sense amplifiers are used as the receivers to restore the full-swing data from the low-swing data signals. Symmetric and mirrored layout topology is adopted to minimize the systematic offset and the NMOS transistors of the cross-coupled inverters are sized large enough to have the desired random offset (calculated using Monte Carlo simulations). The offset of the sense amplifiers is important as it limits the minimum voltage swing on the input wires. Input receivers with gated sense enable signals are used to build the capacitively coupled multiplexers for our low-swing crossbar design.

### 3.1.4 Capacitively Coupled Multiplexers

Capacitively coupled multiplexers use nonlinear capacitances as the switches to drive the long output wires capacitively and exploit the fact that the capacitances of unselected inputs are significantly smaller than the active input capacitance. This enables building fast and efficient multiplexers that can drive long wires with a reduced voltage swing.

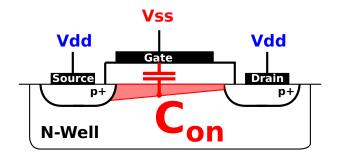

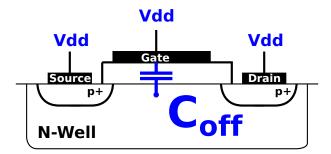

The drain-source connected PMOS capacitances are used as the nonlinear capacitances. As

Figure 3.3: The ON capacitance ratio for drain-source connected PMOS.

Figure 3.4: The OFF capacitance ratio for drain-source connected PMOS.

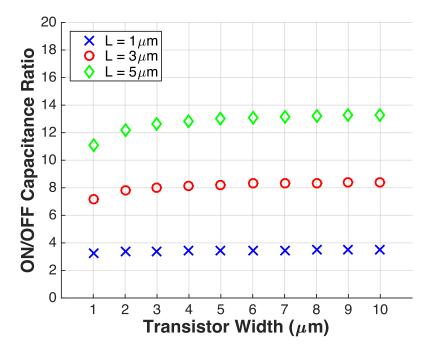

mentioned above, when the PMOS transistor is turned-on, the gate capacitance is large due to the formed channel (Figure 3.3). However, when the transistor is turned-off, the gate capacitance is to the bulk instead of the channel, hence significantly smaller (Figure 3.4). Simulation results in 40nm CMOS bulk showed that the ratio of ON capacitance to the OFF capacitance can be larger than 10X when longer lengths ( $>5\mu$ m) are used for the PMOS transistors. Simulations and our modeling also show that the ratio is more sensitive to the length (L) of the transistors than the width (W) of the transistor, since the on capacitance is strongly proportional to both W and L, whereas the off capacitance is mostly proportional to W of the transistor.

This scheme improves the energy savings by decreasing the coupling capacitance required for the desired voltage swing as well as the savings from the smaller driver and low-swing wires. Assuming load and parasitic capacitances are much smaller than the wire and the coupling capacitances in Equation 3.1, for N:1 multiplexer, the reduced voltage swing can be represented by Equation 3.4 using a nonlinear coupling capacitance ( $C_{on}$  and  $C_{off}$  depending on the state of the transistor).

Figure 3.5: The on to off capacitance ratio for drain-source connected PMOS.

$$V_{swing} = V_{dd} \frac{C_{on}}{C_{on} + (N-1) * C_{off} + C_w}$$

(3.4)

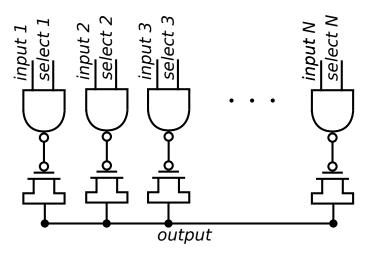

Similar to the scheme used in input data transmitters, NAND gates drive the PMOS capacitances that are connected to the output wire to form the capacitively coupled multiplexer as seen in Fig 3.6. The drain-source of the PMOS capacitance is biased at Vdd. The selected NAND gate's output transitions from high-to-low that turns on the PMOS capacitance, hence achieves a large capacitance to drive the output wire. On the other hand, the unselected NAND gates' outputs stay at Vdd that keeps the PMOS transistors turned-off, hence smaller parasitic load capacitances on the output wire. The output wire is driven via a series capacitance that is the PMOS capacitance of the selected input.

The low-swing output wires also required to be differential and requires twice wire and circuit resources. Only one of the differential data is driven via the series capacitance while the complementary data stays high, hence not increasing the switching energy consumption. This scheme offers as much energy savings as the capacitively coupled wires.

Figure 3.6: Capacitively coupled multiplexer.

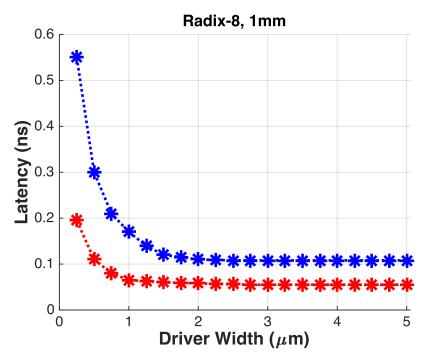

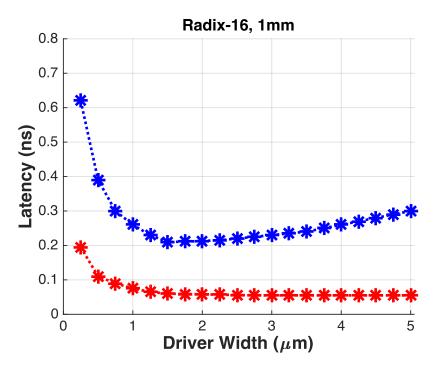

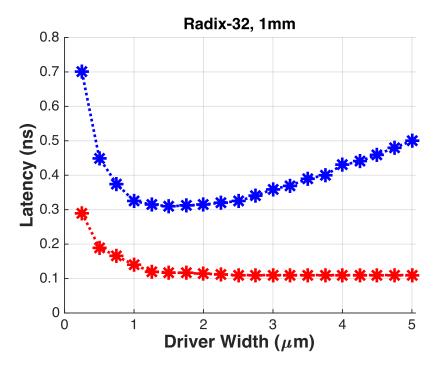

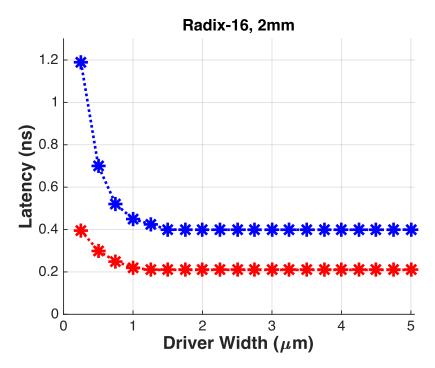

Further, this scheme improves the delay performance due to decreased parasitic loading from the off paths. We compared the latency performance of the capacitively multiplexer to a conventional multiplexer for a crossbar design using 40nm CMOS bulk. The capacitively multiplexer is built to achieve a voltage swing of 200mV (sensed at 100mV) with the corresponding PMOS sizing. Clocked StrongARM sense amplifiers are used to restore the full-swing output data, therefore an extra 30ps (for sense amplifier) and 10% of clock period (for clock skew) is added to the latency of the capacitively coupled multiplexer. On the other hand, the conventional multiplexer is built using tri-state inverters. The inputs for both multiplexers are assumed to be distributed horizontally and the multiplexor switches drive the long output wire as in a crossbar design.